- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371415 > 27174A Versatile I/0: DQ--VI/O and Enhanced--VI/O PDF資料下載

參數(shù)資料

| 型號: | 27174A |

| 英文描述: | Versatile I/0: DQ--VI/O and Enhanced--VI/O |

| 中文描述: | 通用的I / 0:宿舍-六/ O和增強-六/輸出 |

| 文件頁數(shù): | 3/4頁 |

| 文件大?。?/td> | 67K |

| 代理商: | 27174A |

Versatile I/O: DQ–V

I/O

and Enhanced–V

I/O

there could be as much as a 5 ns delay between a con-

trol or clock signal and the data and address signals.

This delay may also occur between the upper and

lower address and/or data lines. To put this in perspec-

tive, if the Flash used in Figure 1 is a 66 MHz Flash, it

could not be safely used at speeds above 50 MHz due

to the uncertainty in the translation buffers’ propagation

delay.

DQ

–

Versatile I/O (DQ

–

V

I/O

)

AMD’s DQ based Versatile I/O (DQ–V

I/O

) follows an old

standard for compatibility with Intel Flash devices and

other legacy devices. This standard calls for the data

pins (DQx) and chip enable (CE#) to be compatible

with the Versatile I/O voltage while all other pins (Ad-

dress, OE#, RY/BY#, etc) still require signaling at V

CC

voltage levels.

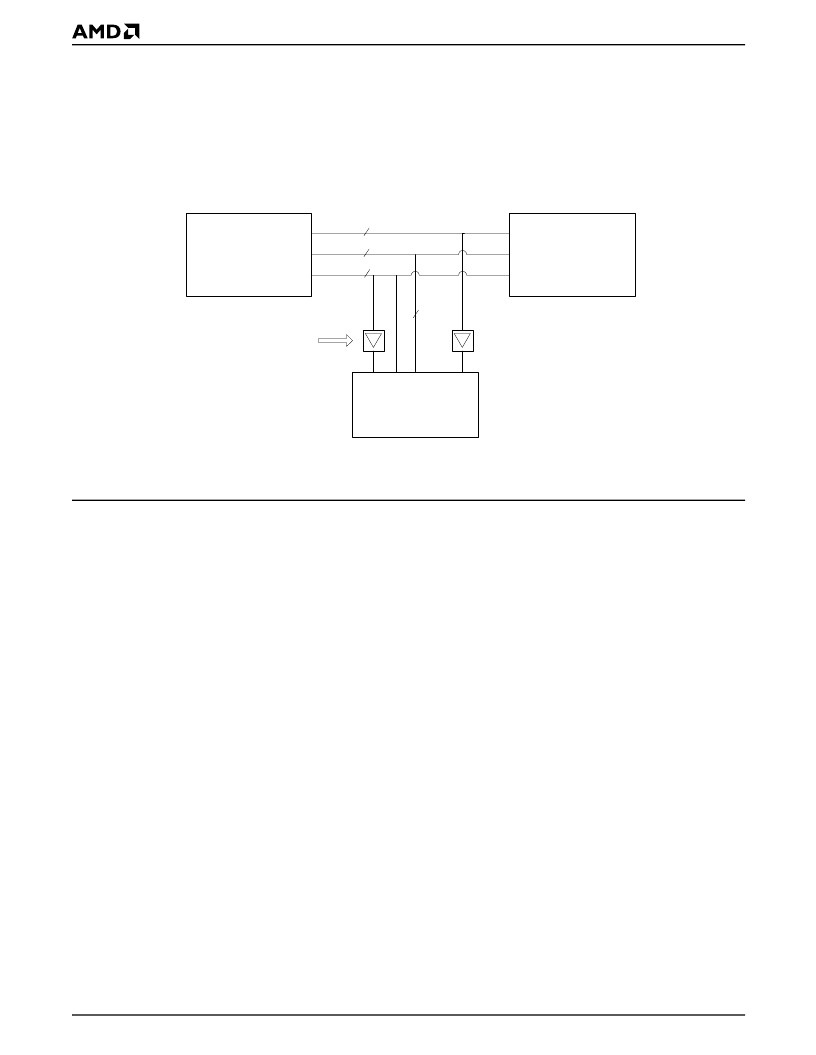

Figure 2.

I/O Signaling to DQ–V

IO

3V Flash with V

IO

= 1.8V

Therefore, as shown in Figure 2, only the data lines and

chip select signals from the microcontroller and Flash

can be connected together directly. The address lines,

OE#, WE#, RESET#, RY/BY#, BYTE#, etc. would

have to pass through voltage translation buffers in

order for the Flash to receive legal high values and to

prevent the microcontroller from being damaged by

3.0V signals from the Flash.

AMD’s DQ–Versatile I/O may at first seem to be of lim-

ited use since only one 16-bit voltage translator is

saved but this small change can greatly increase sys-

tem performance. AMD’s DQ–V

I/O

parts were designed

on the assumption that most high-speed microproces-

sors will assert the address and control lines before

asserting the data lines. By removing the need for volt-

age translation buffers on the data lines and assuming

the address and control lines are asserted half a clock

cycle before the data lines, the clock rate can be in-

creased from 50 MHz to 66 MHz.

Enhanced

–

Versatile I/O (Enhanced

–

V

I/O

)

AMD’s Enhanced–Versatile I/O is similar to the DQ–V

I/

O

, but with the added benefit of having all input and out-

put pins being compatible with the Versatile I/O voltage

and only the internal core memory and logic operating

at the V

CC

voltage.

MicroController

Vcc = 1.8v

Address

Data

Control

x7

x24

DQ-V

I/O

3v

Flash

with V

I/O

= 1.8v

Voltage

Translation

Buffers

Other 1.8v

Devices

32

16

8

16

C

相關PDF資料 |

PDF描述 |

|---|---|

| 2718BD2 | Upo Interface Xfmr |

| 2718BG2 | Upo Interface Xfmr |

| 271KD25NX | 130 to 1000 Volts Varistor 155 to 1100 Joule |

| 271P25.28.F | ±15kV ESD-Protected USB Level Translators in UCSP |

| 279P25.28.F | 2.7Gbps, Low-Power SFP Laser Drivers |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 271-75 | 功能描述:金屬膜電阻器 - 透孔 75ohms 1% 50PPM RoHS:否 制造商:IRC 電阻:63.4 kOhms 容差:1 % 功率額定值:100 mW 電壓額定值:200 V 溫度系數(shù):100 PPM / C 端接類型:Axial 工作溫度范圍: 尺寸:2.3 mm Dia. x 6.4 mm L 封裝:Bulk |

| 271-75.5/AP | 功能描述:金屬膜電阻器 - 透孔 USE 271-75.5/AP-RC 50PPM RoHS:否 制造商:IRC 電阻:63.4 kOhms 容差:1 % 功率額定值:100 mW 電壓額定值:200 V 溫度系數(shù):100 PPM / C 端接類型:Axial 工作溫度范圍: 尺寸:2.3 mm Dia. x 6.4 mm L 封裝:Bulk |

| 271-75.5/AP-RC | 功能描述:金屬膜電阻器 - 透孔 75.5ohms 1% 50PPM RoHS:否 制造商:IRC 電阻:63.4 kOhms 容差:1 % 功率額定值:100 mW 電壓額定值:200 V 溫度系數(shù):100 PPM / C 端接類型:Axial 工作溫度范圍: 尺寸:2.3 mm Dia. x 6.4 mm L 封裝:Bulk |

| 271-75.5/REEL | 功能描述:金屬膜電阻器 - 透孔 75.5ohms 1% 50PPM RoHS:否 制造商:IRC 電阻:63.4 kOhms 容差:1 % 功率額定值:100 mW 電壓額定值:200 V 溫度系數(shù):100 PPM / C 端接類型:Axial 工作溫度范圍: 尺寸:2.3 mm Dia. x 6.4 mm L 封裝:Bulk |

| 271-75.5/REEL-RC | 功能描述:金屬膜電阻器 - 透孔 75.5ohms 1% 50PPM RoHS:否 制造商:IRC 電阻:63.4 kOhms 容差:1 % 功率額定值:100 mW 電壓額定值:200 V 溫度系數(shù):100 PPM / C 端接類型:Axial 工作溫度范圍: 尺寸:2.3 mm Dia. x 6.4 mm L 封裝:Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。