- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371434 > 28F002BV-B (Intel Corp.) 2-MBIT SmartVoltage BOOT BLOCK FLASH MEMORY FAMILY PDF資料下載

參數(shù)資料

| 型號: | 28F002BV-B |

| 廠商: | Intel Corp. |

| 英文描述: | 2-MBIT SmartVoltage BOOT BLOCK FLASH MEMORY FAMILY |

| 中文描述: | 2兆位SmartVoltage啟動塊閃存系列 |

| 文件頁數(shù): | 10/37頁 |

| 文件大小: | 455K |

| 代理商: | 28F002BV-B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

28F002BC 2-MBIT BOOT BLOCK FLASH MEMORY

E

10

PRELIMINARY

1.5

Pin Descriptions

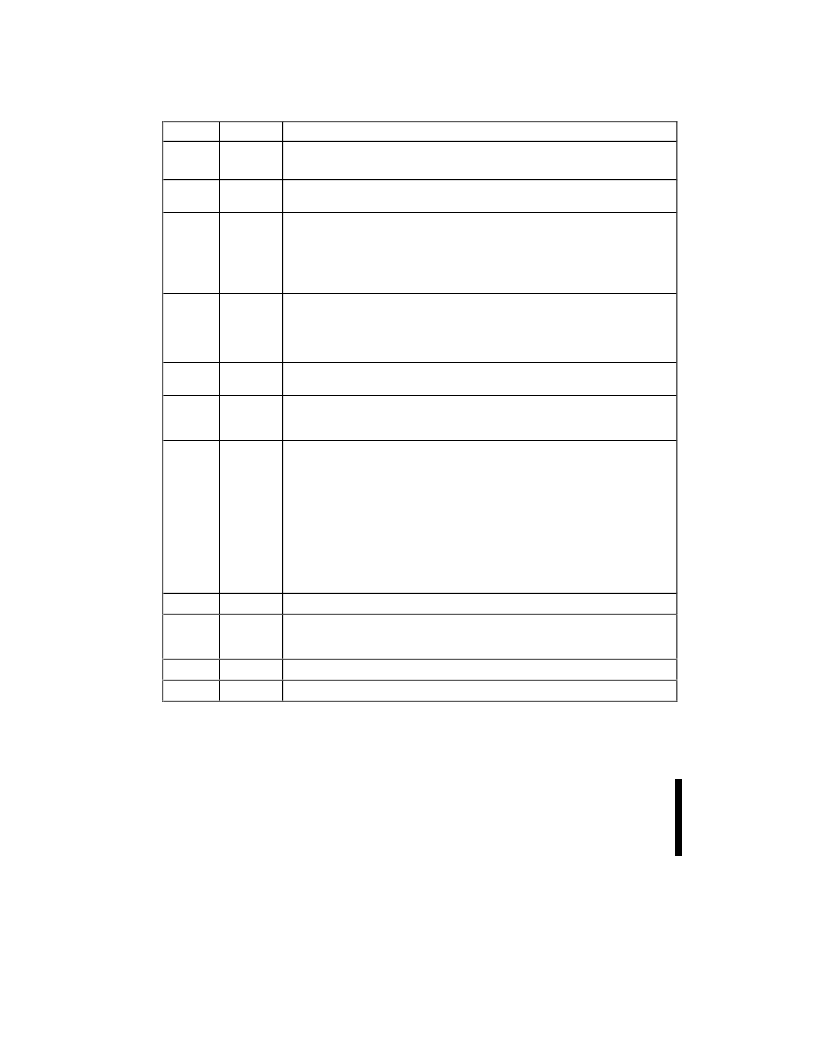

Table 1. 28F002BC Pin Descriptions

Symbol

Type

Name and Function

A

–1

,

A

0

–A

17

INPUT

ADDRESS INPUTS

for memory addresses. Addresses are internally latched

during a write cycle. A

-1

is used on the PSOP package only. A

17

is used on the

TSOP and PDIP packages.

ADDRESS INPUT:

When A

9

is at V

HH,

the signature mode is accessed. During

this mode, A

0

decodes between the manufacturer and device IDs.

A

9

INPUT

DQ

0

–

DQ

7

INPUT/

OUTPUT

DATA INPUTS/OUTPUTS:

Inputs array data on the second CE# and WE#

cycle during a program operation. Inputs commands to the Command User

Interface when CE# and WE# are active. Data is internally latched during the

write cycle. Outputs array, Intelligent Identifier and Status register data. The

data pins float to tri-state when the chip is de-selected or the outputs are

disabled.

CE#

INPUT

CHIP ENABLE:

Activates the device’s control logic, input buffers, decoders and

sense amplifiers. CE# is active low. CE# high deselects the memory device and

reduces power consumption to standby levels. If CE# and RP# are high, but not

at a CMOS high level, the standby current will increase due to current flow

through the CE# and RP# input stages.

OE#

INPUT

OUTPUT ENABLE:

Enables the device’s outputs through the data buffers

during a read cycle. OE# is active low.

WE#

INPUT

WRITE ENABLE:

Controls writes to the Command Register and array blocks.

WE# is active low. Addresses and data are latched on the rising edge of the

WE# pulse.

RP#

INPUT

RESET/DEEP POWER-DOWN:

Provides three-state control. Puts the device in

deep power-down mode, locks, and unlocks the boot block from program/erase.

When RP# is at logic high level (6.5V maximum), the boot block is locked and

cannot be programmed or erased.

When RP# = V

(11.4V minimum ), the boot block is unlocked and can be

programmed or erased.

When RP# is at a logic low level the boot block is locked, the deep power-down

mode is enabled and the WSM is reset—preventing any blocks from being

programmed or erased. When RP# transitions from logic low to logic high, the

flash memory enters the read array mode.

V

CC

DEVICE POWER SUPPLY:

5.0V

±

10%, 5.0V ± 5%

V

PP

PROGRAM/ERASE POWER SUPPLY:

For erasing memory array blocks or

programming data in each block. When V

PP

< V

PPLK

all blocks are locked and

memory contents cannot be altered.

GND

GROUND:

For all internal circuitry.

NC

NO CONNECT:

Pin may be driven or left floating.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 28F004B3 | 3 Volt Advanced Boot Block Flash Memory(3 V,4M位高級引導(dǎo)塊閃速存儲器) |

| 28F004S3 | BYTE-WIDE SMART 3 FlashFile MEMORY FAMILY 4, 8, AND 16 MBIT |

| 28F004S5 | BYTE-WIDE SMART 5 FlashFile MEMORY FAMILY 4, 8, AND 16 MBIT |

| 28F004SC | BYTE-WIDE SmartVoltage FlashFile MEMORY FAMILY 4, 8, AND 16 MBIT |

| 28F008B3 | SMART 3 ADVANCED BOOT BLOCK BYTE-WIDE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 28F002BV-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2-MBIT SmartVoltage BOOT BLOCK FLASH MEMORY FAMILY |

| 28F002BV-T/B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SmartVoltage Boot Block Flash Memory Fa |

| 28F002BX-B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:28F002BX-B - 2-MBIT (128K x 16. 256K x 8) BOOT BLOCK FLASH MEMORY FAMILY |

| 28F002BX-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:28F002BX-T - 2-MBIT (128K x 16. 256K x 8) BOOT BLOCK FLASH MEMORY FAMILY |

| 28F004B5 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SMART 5 BOOT BLOCK. FLASH MEMORY FAMILY 2. 4. 8 MBIT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。