- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67328 > 5962-8967901XX (CIRRUS LOGIC INC) 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CQCC44 PDF資料下載

參數(shù)資料

| 型號: | 5962-8967901XX |

| 廠商: | CIRRUS LOGIC INC |

| 元件分類: | ADC |

| 英文描述: | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CQCC44 |

| 封裝: | CERAMIC, LCC-44 |

| 文件頁數(shù): | 41/50頁 |

| 文件大?。?/td> | 520K |

| 代理商: | 5962-8967901XX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁當前第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁

Reset/Self-Calibration Modes

The A/D converter will usually reset itself upon

power-up. Since this function is not guaranteed,

the converter must be reset upon power-up in

system operation. The converter can be reset on

the CDB5012, CDB5012A, CDB5014, CDB5016

board by momentarily depressing push-button

SW-2 thus initiating a full calibration cycle;

1,443,840 master clock cycles later the converter

is ready for normal operation.

The converters also feature two other calibration

modes: burst and interleave. The use of Burst

calibration is not recommended. Interleave can be

initiated by setting switch position 3 to the on

position. In the interleave mode (INTRLV low),

the converter appends one small portion of a cali-

bration cycle (20 master clock cycles) to each

conversion cycle. Thus, a full calibration cycle

completes every 72,192 conversion cycles. The

Interleave calibration mode should not be used

intermittently.

A more detailed discussion of the converters’

calibration modes and capabilities can be found

in their data sheets.

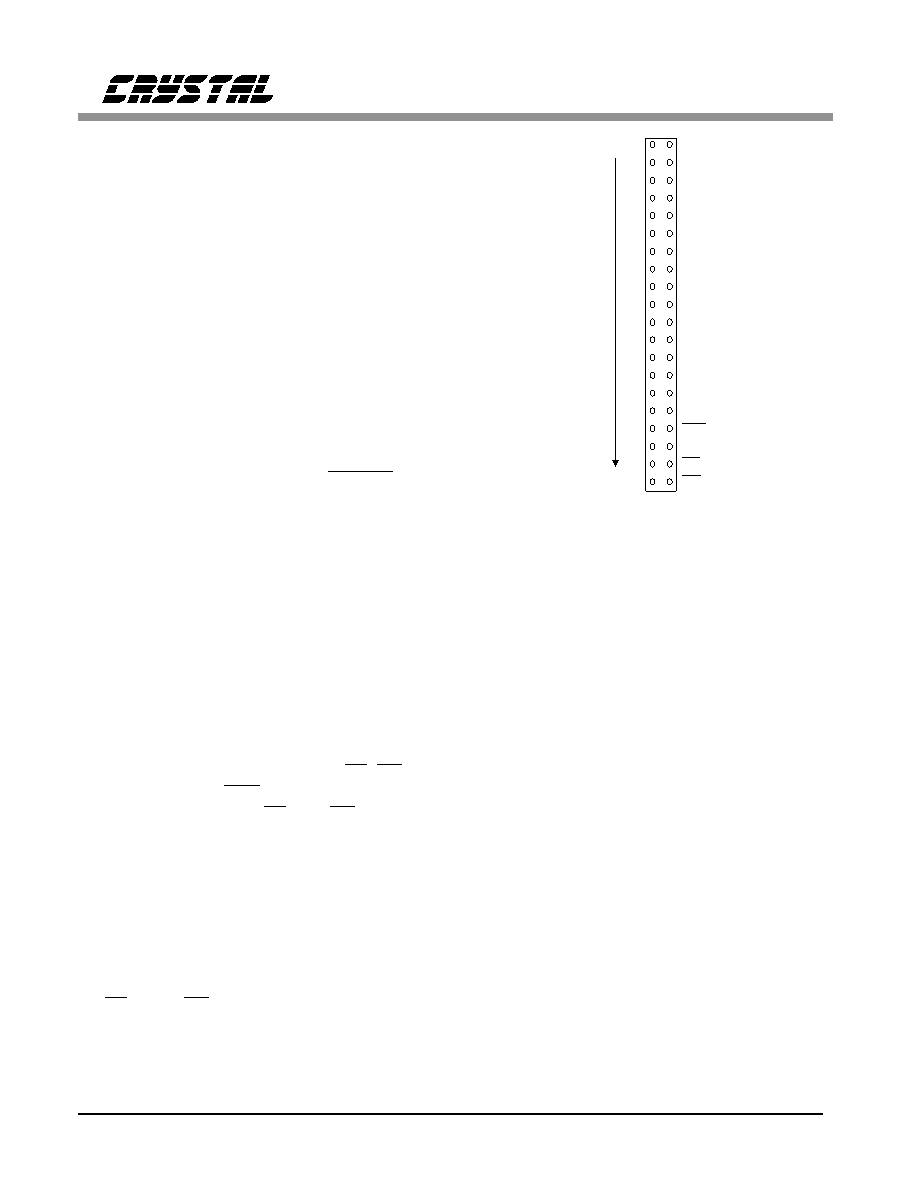

Parallel Output Data/Microprocessor Interface

The converter’s outputs D0-D15, its CS, RD, and

A0 inputs, and its EOC output are available at

the 40 pin header. The CS and RD inputs are

pulled low through 10 k

resistors placing

the converter in a microprocessor-independent

mode. Control input A0 is pulled up, insuring the

converter’s output word, rather than the status

register, appears at the header.

The converter’s 3-state output buffers and micro-

processor interface can be exercised by driving

the CS and/or RD inputs at the header. Similarly,

the converter’s 8-bit status register can be ob-

tained on D0-D7 by driving A0 low.

The converter’s EOC and data outputs are not

b u ffe re d on the CDB 501 2, CDB 501 2A,

CDB5014, CDB5016. Therefore, careful attention

should be paid to the load presented by any ca-

bling, especially if the 3-state output buffers are

to be exercised at speed. Twisted ribbon cable is

typically specified at 10pF/ft, so several feet can

generally be accommodated.

Serial Output Data

Serial output data is available at the two BNC

connections SCLK and SDATA. Data appears

MSB first, LSB last, and is valid on the rising

edge of SCLK.

Master Clock

The A/D converter operates from a master clock

which can either be internally-generated or exter-

nally-supplied. For operation with an external

clock, the BNC connector labeled CLKIN

should be driven with a TTL clock signal. The

CDB5012, CDB5012A, CDB5014, CDB5016 is

shipped from the factory with the CLKIN input

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

A0

RD

D10

D11

D12

D13

D14

D15

EOC

CS

DGND

Figure 4. Header Pin Definitions

CDB5012A, CDB5014, CDB5016

46

DS14DB11

相關PDF資料 |

PDF描述 |

|---|---|

| 5962-8967402XX | 1-CH 14-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CQCC44 |

| 5962-8967401QX | 1-CH 14-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CDIP40 |

| 5962-8967401XX | 1-CH 14-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CQCC44 |

| 5962-8967901QX | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CDIP40 |

| 5962-8967602XX | 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CQCC44 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 5962-89680012A | 制造商:Texas Instruments 功能描述:Octal Transmitter/Receiver 20-Pin LCCC Tube |

| 5962-89680012A-T | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

| 5962-8968001RA | 制造商:Texas Instruments 功能描述:Octal Transmitter/Receiver 20-Pin CDIP Tube 制造商:Texas Instruments 功能描述:LINE TRNSCVR 8TR 8TX 8RX 20CDIP - Rail/Tube |

| 5962-8968001SA | 制造商:Texas Instruments 功能描述:Octal Transmitter/Receiver 20-Pin CFPAK Tube 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| 5962-89681012A | 制造商:Rochester Electronics LLC 功能描述: 制造商:Texas Instruments 功能描述:55ALS161, AVAIL AS SMD ONLY, RERELEASE - Rail/Tube 制造商:Texas Instruments 功能描述:Octal Transmitter/Receiver IEEE-488 20-Pin LCCC Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復。