- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67330 > 5962-9064202QRA (TEXAS INSTRUMENTS INC) 11-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, CDIP20 PDF資料下載

參數(shù)資料

| 型號(hào): | 5962-9064202QRA |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 11-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, CDIP20 |

| 封裝: | CERAMIC, DIP-20 |

| 文件頁(yè)數(shù): | 2/32頁(yè) |

| 文件大小: | 770K |

| 代理商: | 5962-9064202QRA |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)

www.ti.com

SLAS052G – MARCH 1992 – REVISED JANUARY 2006

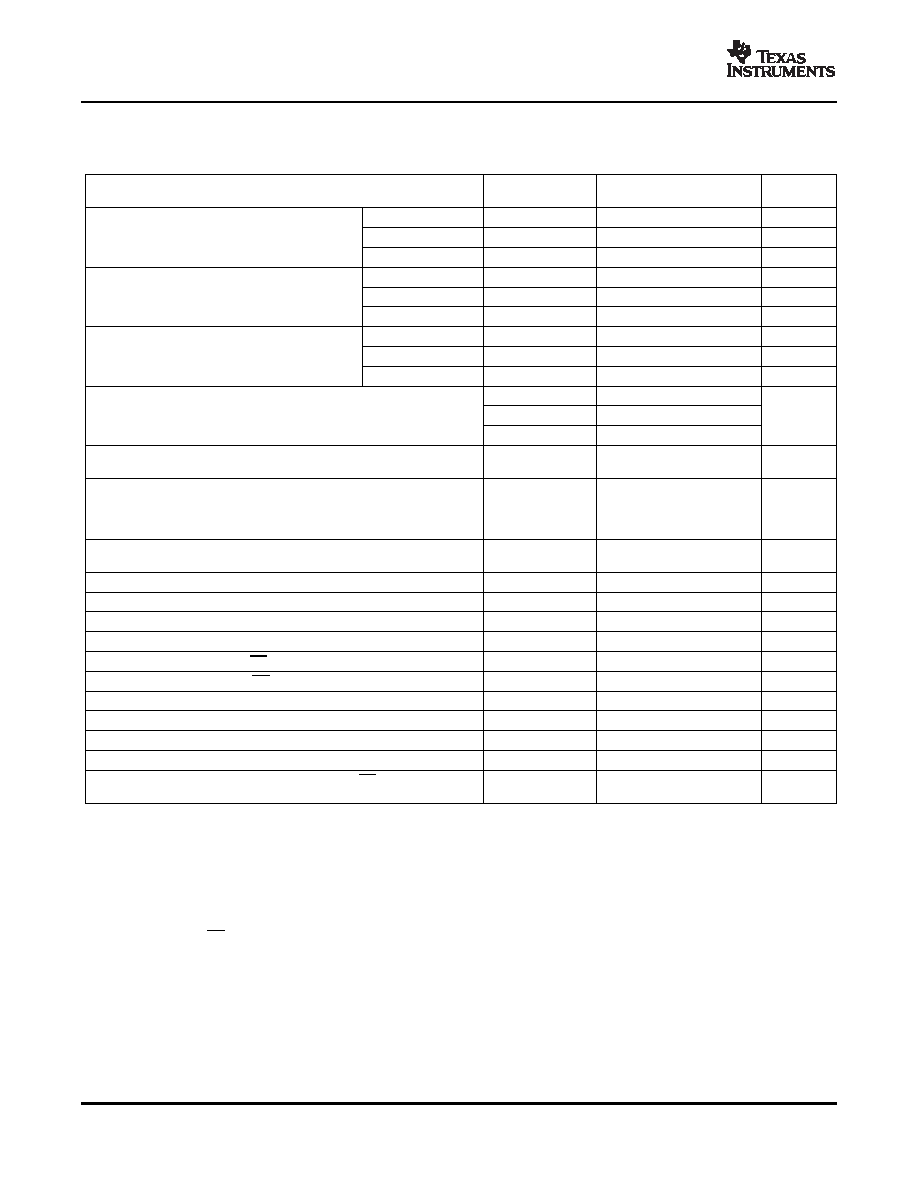

OPERATING CHARACTERISTICS (continued)

over recommended operating free-air temperature range, V

CC = Vref+ = 4.5 V to 5.5 V, I/O CLOCK frequency = 2.1 MHz

(unless otherwise noted)

TEST

MIN

TYP (1)

MAX

UNIT

CONDITIONS

TLC1542C, I, or Q

See (4)

±1

LSB

EZS

Zero-scale error, see (3)

TLC1543C, I, or Q

See (4)

±1

LSB

TLC1542M

See (4)

±1

LSB

TLC1542C, I, or Q

See (4)

±1

LSB

EFS

Full-scale error, see (3)

TLC1543C, I, or Q

See (4)

±1

LSB

TLC1542M

See (4)

±1

LSB

TLC1542C, I, or Q

±1

LSB

Total unadjusted error, see (5)

TLC1543C, I, or Q

±1

LSB

TLC1542M

±1

LSB

ADDRESS = 1011

512

Self-test output code, see Table 3 and (6)

ADDRESS = 1100

0

ADDRESS = 1101

1023

See timing

tconv

Conversion time

21

s

diagrams

21

See timing

+10 I/O

tc

Total cycle time (access, sample, and conversion)

s

diagrams and (7)

CLOCK

periods

See timing

I/O CLOCK

tacq

Channel acquisition time (sample)

6

diagrams and (7)

periods

tv

Valid time, DATA OUT remains valid after I/O CLOCK

↓ See Figure 6

10

ns

td(I/O-DATA)

Delay time, I/O CLOCK

↓ to DATA OUT valid

See Figure 6

240

ns

td(I/O-EOC)

Delay time, tenth I/O CLOCK

↓ to EOC↓

See Figure 7

70

240

ns

td(EOC-DATA)

Delay time, EOC

↑ to DATA OUT (MSB)

See Figure 8

100

ns

tPZH, tPZL

Enable time, CS

↓ to DATA OUT (MSB driven)

See Figure 3

1.3

s

tPHZ, tPLZ

Disable time, CS

↑ to DATA OUT (high impedance)

See Figure 3

150

ns

tr(EOC)

Rise time, EOC

See Figure 8

300

ns

tf(EOC)

Fall time, EOC

See Figure 7

300

ns

tr(DATA)

Rise time, data bus

See Figure 6

300

ns

tf(DATA)

Fall time, data bus

See Figure 6

300

ns

Delay time, tenth I/O CLOCK

↓ to CS↓ to abort

td(I/O-CS)

9

s

conversion (see Note (8))

(3)

Zero-scale error is the difference between 0000000000 and the converted output for zero input voltage; full-scale error is the difference

between 1111111111 and the converted output for full-scale input voltage.

(4)

Analog input voltages greater than that applied to REF+ convert as all ones (1111111111), while input voltages less than that applied to

REF- convert as all zeros (0000000000). The device is functional with reference voltages down to 1 V (Vref+-Vref-); however, the

electrical specifications are no longer applicable.

(5)

Total unadjusted error comprises linearity, zero-scale, and full-scale errors.

(6)

Both the input address and the output codes are expressed in positive logic.

(7)

I/O CLOCK period = 1/(I/O CLOCK frequency) (see Figure 6)

(8)

Any transitions of CS are recognized as valid only if the level is maintained for a setup time plus two falling edges of the internal clock

(1.425

s) after the transition.

10

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5962-9064202Q2A | 11-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, CQCC20 |

| TLC1542QFN | 11-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PQCC20 |

| TLC1542CFN | 11-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PQCC20 |

| TLC1542CN | 11-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDIP20 |

| TLC1542CDW | 11-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 5962-9065002PA | 制造商:Texas Instruments 功能描述:LDO Cntrlr REG 2.5V to 35V 8-Pin CDIP |

| 5962-9065101MCA | 制造商:Texas Instruments 功能描述:Buffer/Line Driver 4-CH Non-Inverting 3-ST CMOS 14-Pin CDIP Tube |

| 5962-9065201MEA | 制造商:Texas Instruments 功能描述:Multiplexer 1-Element CMOS 8-IN 16-Pin CDIP Tube 制造商:Texas Instruments 功能描述:MLTPLXR 1-ELEM CMOS 8-IN 16CDIP - Rail/Tube |

| 5962-9065401MEA | 制造商:Texas Instruments 功能描述:Analog Multiplexer Single 8:1 16-Pin CDIP Tube 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述:CD54HCT4051F3A - Rail/Tube |

| 59629065801KA | 制造商:WSI 功能描述:New |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。