- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67343 > 5962-9957001QRA (TEXAS INSTRUMENTS INC) 4-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, CDIP20 PDF資料下載

參數(shù)資料

| 型號(hào): | 5962-9957001QRA |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 4-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, CDIP20 |

| 封裝: | CERDIP-20 |

| 文件頁(yè)數(shù): | 13/47頁(yè) |

| 文件大?。?/td> | 764K |

| 代理商: | 5962-9957001QRA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)

TLV2544, TLV2548

2.7 V TO 5.5 V, 12-BIT, 200 KSPS, 4/8 CHANNEL, LOW POWER,

SERIAL ANALOG-TO-DIGITAL CONVERTERS WITH AUTO POWER DOWN

SLAS198A –FEBRUARY 1999– REVISED AUGUST 1999

20

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

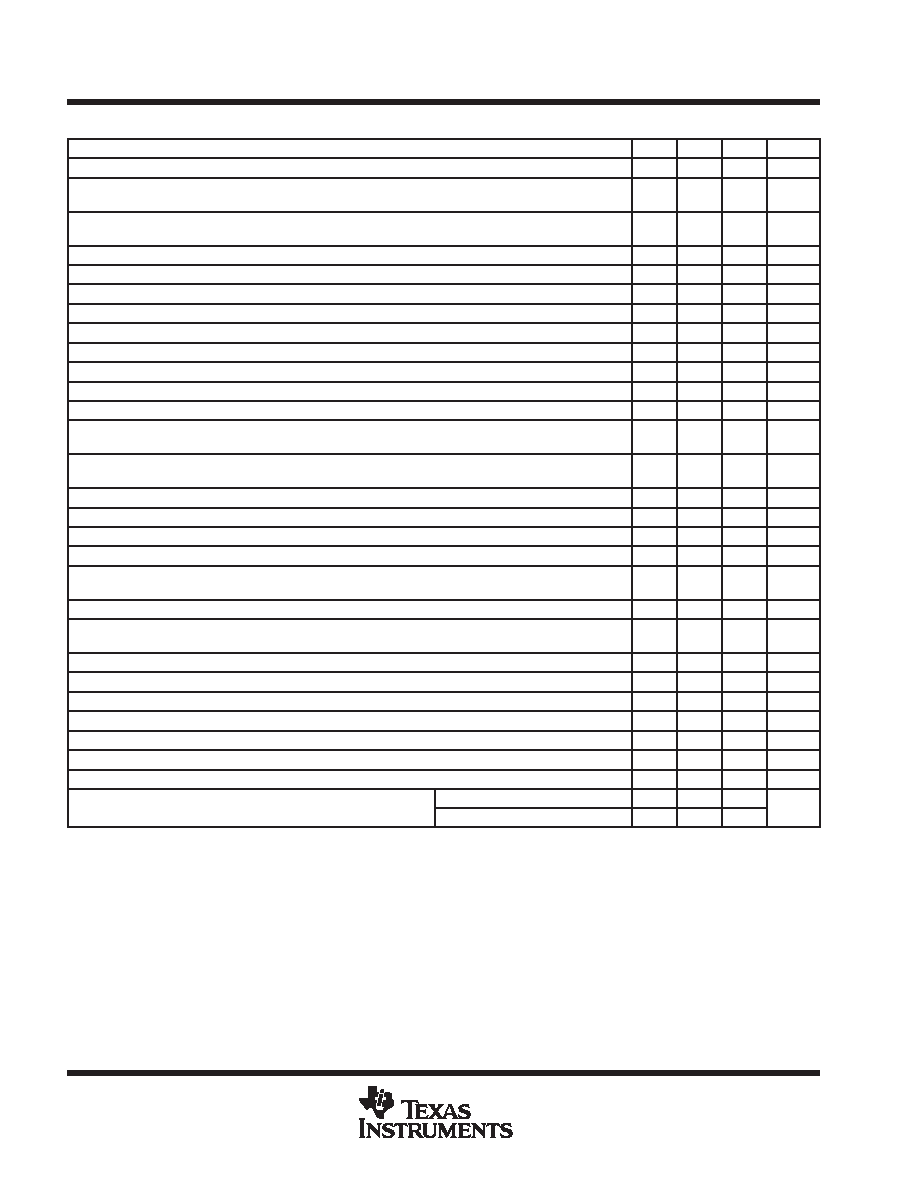

recommended operating conditions (continued)

MIN

NOM

MAX

UNIT

Transition time, for FS, SCLK, SDI, tt(SCLK)

0.5

SCLK

Setup time, CS falling edge before SCLK rising edge (FS=1) or before SCLK falling edge (when FS is active),

tsu(CS-SCLK)

0.5

SCLK

Hold time, CS rising edge after SCLK rising edge (FS=1) or after SCLK falling edge (when FS is active),

th(SCLK-CS)

5

ns

Delay time, delay from CS falling edge to FS rising edge, td(CSL-FSH)

0.5

7

SCLKs

Delay time, delay time from 16th SCLK falling edge to CS rising edge (FS is active), td(SCLK16L-CSH)

0.5

SCLKs

Setup time, FS rising edge before SCLK falling edge, tsu(FSH-SCLKL)

0.25

0.75

SCLKs

Hold time, FS hold high after SCLK falling edge, th(FSH-SCLKL)

0.25

0.75

SCLKs

Pulse width, CS high time, twH(CS)

100

ns

SCLK cycle time, VCC = 2.7 V to 3.6V, tc(SCLK)

67

ns

SCLK cycle time, VCC = 4.5 V to 5.5V, tc(SCLK)

50

ns

Pulse width, SCLK low time, twL(SCLK)

20

30

ns

Pulse width, SCLK high time, twH(SCLK)

20

30

ns

Setup time, SDI valid before falling edge of SCLK (FS is active) or the rising edge of SCLK (FS=1),

tsu(DI-SCLK)

25

ns

Hold time, SDI hold valid after falling edge of SCLK (FS is active) or the rising edge of SCLK (FS=1),

th(DI-SCLK)

5

ns

Delay time, delay from CS falling edge to SDO valid, td(CSL-DOV)

1

25

ns

Delay time, delay from FS falling edge to SDO valid, td(FSL-DOV)

1

25

ns

Delay time, delay from SCLK rising edge (FS is active) or SCLK falling edge (FS=1) SDO valid, td(SCLK-DOV)

1

25

ns

Delay time, delay from CS rising edge to SDO 3-stated, td(CSH-DOZ)

1

25

ns

Delay time, delay from 16th SCLK falling edge (FS is active) or the 16th rising edge (FS=1) to EOC falling

edge, td(SCLK-EOCL)

1

25

ns

Delay time, delay from EOC rising edge to SDO 3-stated if CS is low, td(EOCH-DOZ)

1

50

ns

Delay time, delay from 16th SCLK rising edge to INT falling edge (FS =1) or from the 16th falling edge SCLK

to INT falling edge (when FS active), td(SCLK-INTL)

3.5

s

Delay time, delay from CS falling edge to INT rising edge, td(CSL-INTH)

1

50

ns

Delay time, delay from CS rising edge to CSTART falling edge, td(CSH-CSTARTL)

100

ns

Delay time, delay from CSTART rising edge to EOC falling edge, td(CSTARTH-EOCL)

1

50

ns

Pulse width, CSTART low time, twL(CSTART)

0.8

s

Delay time, delay from CS rising edge to EOC rising edge, td(CSH-EOCH)

1

50

ns

Delay time, delay from CSTART rising edge to CSTART falling edge, td(CSTARTH-CSTARTL)

3.6

s

Delay time, delay from CSTART rising edge to INT falling edge, td(CSTARTH-INTL)

3.5

s

Operating free air temperature TA

TLV2544C/TLV2548C

0

70

_C

Operating free-air temperature, TA

TLV2544I/TLV2548I

–40

85

_C

NOTE 2: This is the time required for the clock input signal to fall from VIH max or to rise from VILmax to VIHmin. In the vicinity of normal room

temperature, the devices function with input clock transition time as slow as 1

s for remote data-acquisition applications where the

sensor and A/D converter are placed several feet away from the controlling microprocessor.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV2548MJ | 4-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, CDIP20 |

| 5962-9957601Q2A | SERIAL INPUT LOADING, 3.5 us SETTLING TIME, 12-BIT DAC, CQCC20 |

| 5962-9957601QPA | SERIAL INPUT LOADING, 3.5 us SETTLING TIME, 12-BIT DAC, CDIP8 |

| TLV5638CDR | SERIAL INPUT LOADING, 3.5 us SETTLING TIME, 12-BIT DAC, PDSO8 |

| TLV5638CD | SERIAL INPUT LOADING, 3.5 us SETTLING TIME, 12-BIT DAC, PDSO8 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 5962-9957601Q2A | 制造商:Texas Instruments 功能描述:5962-9957601Q2A - Rail/Tube |

| 5962-9957601QPA | 功能描述:數(shù)模轉(zhuǎn)換器- DAC 12B1 or 3.5 us DAC Serial InpDual DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時(shí)間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| 5962-9957701NXD | 制造商:Texas Instruments 功能描述:THS1206MDAB, ADC, 12BITSERIAL, 6MSPS - Rail/Tube |

| 5962-9958101QXC | 功能描述:LVDS 接口集成電路 RoHS:否 制造商:Texas Instruments 激勵(lì)器數(shù)量:4 接收機(jī)數(shù)量:4 數(shù)據(jù)速率:155.5 Mbps 工作電源電壓:5 V 最大功率耗散:1025 mW 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-16 Narrow 封裝:Reel |

| 5962-9958301Q2A | 制造商:Texas Instruments 功能描述:DC DC Cntrlr Single-OUT PWM DC to DC Controller 3.6V to 40V Input 20-Pin LCCC Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。