- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄366245 > 65C256 (Electronic Theatre Controls, Inc.) 32K x 8 LOW POWER CMOS STATIC RAM PDF資料下載

參數(shù)資料

| 型號(hào): | 65C256 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 32K x 8 LOW POWER CMOS STATIC RAM |

| 中文描述: | 32K的× 8低功耗CMOS靜態(tài)RAM |

| 文件頁(yè)數(shù): | 1/11頁(yè) |

| 文件大?。?/td> | 74K |

| 代理商: | 65C256 |

Integrated Silicon Solution, Inc. — www.issi.com —

1-800-379-4774

Rev. A

03/24/04

1

IS65C256

ISSI

Copyright 2004 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability

arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any

published information and before placing orders for products.

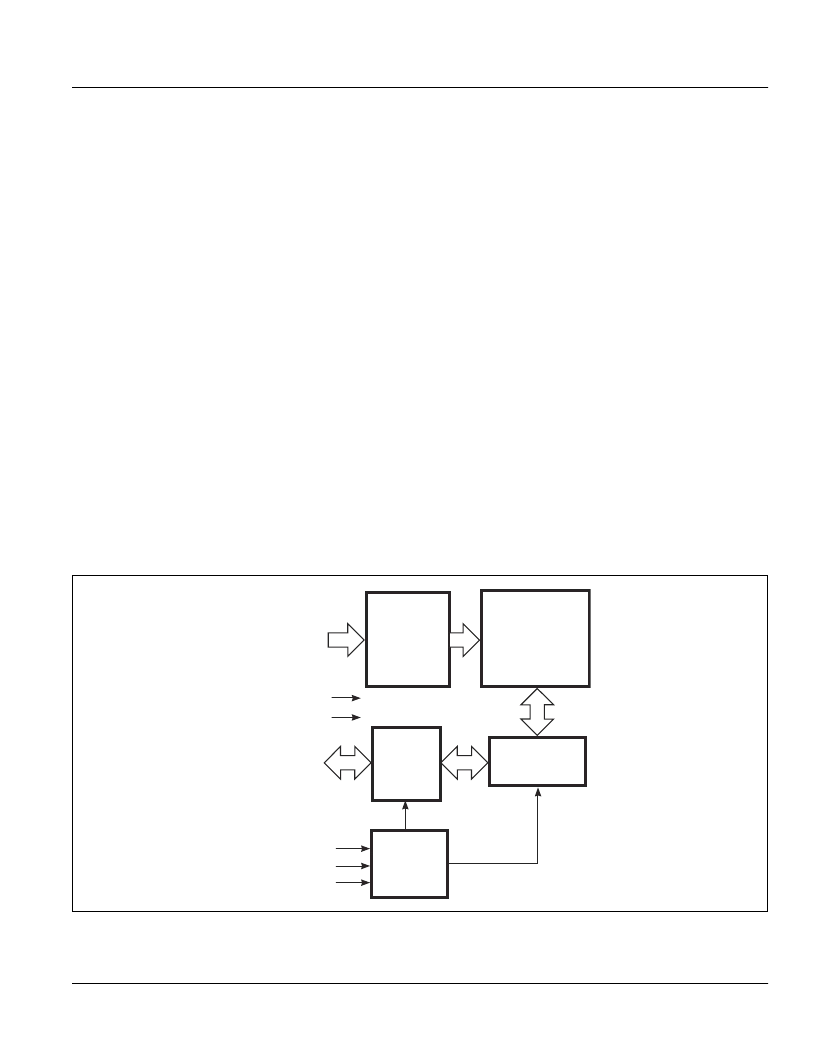

FUNCTIONAL BLOCK DIAGRAM

32K x 8 LOW POWER CMOS

STATIC RAM

FEATURES

High-speed access time: 20 ns

Low active power: 200 mW (typical)

Low standby power:

250 μW (typical) CMOS standby

Fully static operation: no clock or refresh

required

TTL compatible inputs and outputs

Single 5V power supply

Temperature Offerings:

Option A1: –40

o

C to +85

o

C

Option A2: –40

o

C to +105

o

C

Option A3: –40

o

C to +125

o

C

MARCH 2004

DESCRIPTION

The ISSI IS65C256 is a low power, 32,768 word by 8-bit

CMOS static RAM. It is fabricated using ISSIs high-

performance, low power CMOS technology.

When CS is HIGH (deselected), the device assumes a

standby mode at which the power dissipation can be

reduced down to 250 μW (typical) at CMOS input levels.

Easy memory expansion is provided by using an active

LOW Chip Select (CS) input and an active LOW Output

Enable (OE) input. The active LOW Write Enable (WE)

controls both writing and reading of the memory.

The IS65C256 is Packaged in the JEDEC Standard 28-Pin

SOP and 28-Pin TSOP (Type I).

A0-A14

CS

OE

WE

32K X 8

MEMORY ARRAY

DECODER

COLUMN I/O

CONTROL

CIRCUIT

GND

V

DD

I/O

DATA

CIRCUIT

I/O0-I/O7

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 65PWB31 | DOD-PD-0734 (2nd edition) |

| 6609048-4 | Power LIne Q Series |

| 6609048-5 | Power LIne Q Series |

| 6609048-7 | Power LIne Q Series |

| 6609049-1 | Power LIne Q Series |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 65C4321FS | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 65C4993FS | 制造商: 功能描述: |

| 65C500V300AS | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 65C66R5F | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 65C7 | 制造商:MISCELLANEOUS MANUFACTURERS 功能描述:MISCELLANEOUS TUBES |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。