- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄68812 > 73S1210F-68IMR/F (MAXIM INTEGRATED PRODUCTS INC) 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, QCC68 PDF資料下載

參數(shù)資料

| 型號(hào): | 73S1210F-68IMR/F |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | 電源管理 |

| 英文描述: | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, QCC68 |

| 封裝: | LEAD FREE, QFN-68 |

| 文件頁數(shù): | 32/126頁 |

| 文件大小: | 1231K |

| 代理商: | 73S1210F-68IMR/F |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁

DS_1210F_001

73S1210F Data Sheet

Rev. 1.4

13

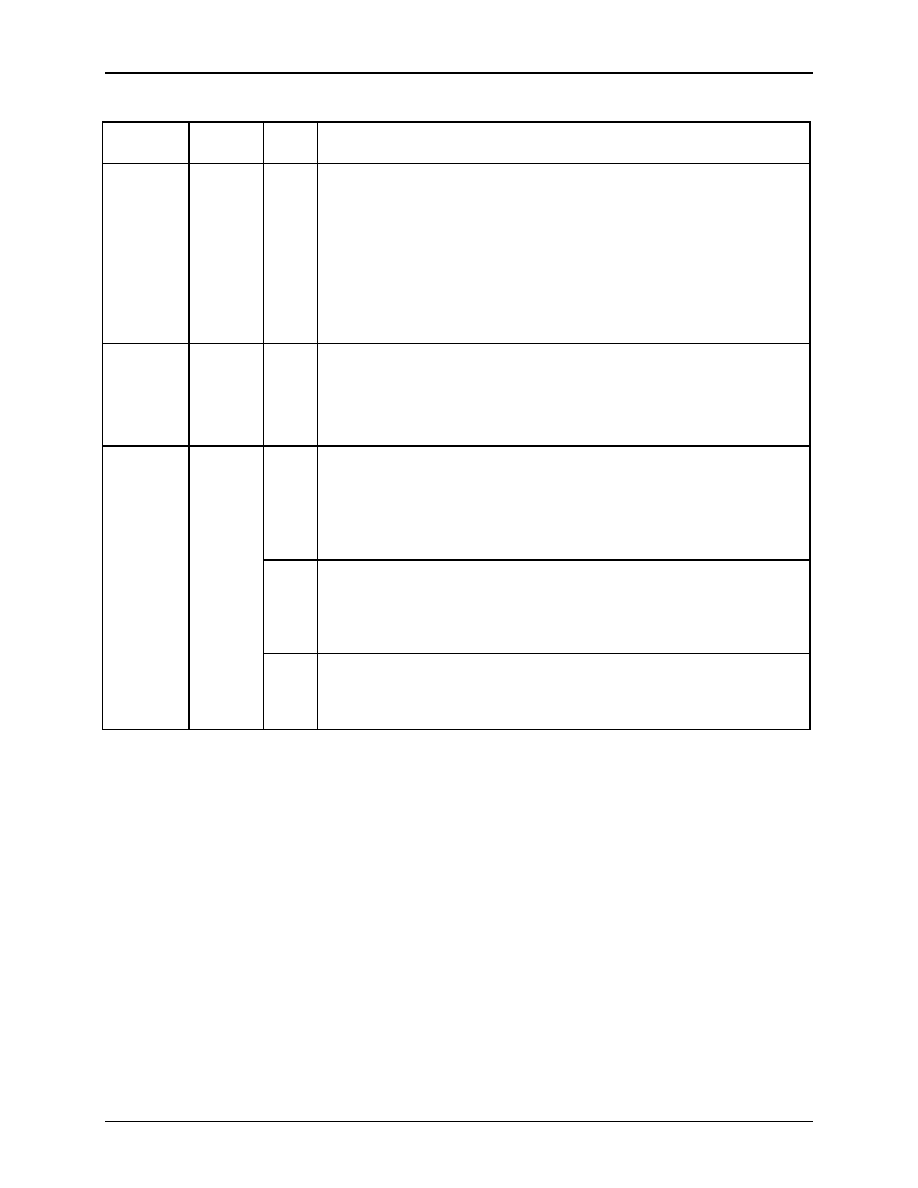

Table 3: Flash Special Function Registers

Register

SFR

Address

R/W

Description

ERASE

0x94

W

This register is used to initiate either the Flash Mass Erase cycle or the

Flash Page Erase cycle. Specific patterns are expected for ERASE in

order to initiate the appropriate Erase cycle (default = 0x00).

0x55 – Initiate Flash Page Erase cycle. Must be proceeded by a write

to PGADDR @ SFR 0xB7.

0xAA – Initiate Flash Mass Erase cycle. Must be proceeded by a write

to FLSH_MEEN @ SFR 0xB2 and the debug port must be

enabled.

Any other pattern written to ERASE will have no effect.

PGADDR

0xB7

R/W

Flash Page Erase Address register containing the flash memory page

address (page 0 through 127) that will be erased during the Page Erase

cycle (default = 0x00). Note: the page address is shifted left by one bit

(see detailed description above).

Must be re-written for each new Page Erase cycle.

FLSHCTL

0xB2

R/W

Bit 0 (FLSH_PWE): Program Write Enable:

0 – MOVX commands refer to XRAM Space, normal operation (default).

1 – MOVX @DPTR,A moves A to Program Space (Flash) @ DPTR.

This bit is automatically reset after each byte written to flash. Writes to

this bit are inhibited when interrupts are enabled.

W

Bit 1 (FLSH_MEEN): Mass Erase Enable:

0 – Mass Erase disabled (default).

1 – Mass Erase enabled.

Must be re-written for each new Mass Erase cycle.

R/W

Bit 6 (SECURE):

Enables security provisions that prevent external reading of flash

memory and CE program RAM. This bit is reset on chip reset and may

only be set. Attempts to write zero are ignored.

Internal Data Memory: The Internal data memory provides 256 bytes (0x00 to 0xFF) of data memory.

The internal data memory address is always one byte wide and can be accessed by either direct or

indirect addressing. The Special Function Registers occupy the upper 128 bytes. This SFR area is

available only by direct addressing. Indirect addressing accesses the upper 128 bytes of Internal

RAM.

The lower 128 bytes contain working registers and bit-addressable memory. The lower 32 bytes form

four banks of eight registers (R0-R7). Two bits on the program memory status word (PSW) select which

bank is in use. The next 16 bytes form a block of bit-addressable memory space at bit addresses 0x00-

0x7F. All of the bytes in the lower 128 bytes are accessible through direct or indirect addressing. Table 4

shows the internal data memory map.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 73S1210F-44IM/F | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, QCC44 |

| 73S8009C-20IMR/F | 1-CHANNEL POWER SUPPLY SUPPORT CKT, QCC20 |

| 73S8009C-20IM/F | 1-CHANNEL POWER SUPPLY SUPPORT CKT, QCC20 |

| 73S8009C-32IM/F | POWER SUPPLY SUPPORT CKT, QCC32 |

| 73S8009C-32IMR/F | POWER SUPPLY SUPPORT CKT, QCC32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 73S1210F-68M/F/PB | 制造商:Maxim Integrated Products 功能描述:- Trays |

| 73S1210F-68M/F/PG | 功能描述:8位微控制器 -MCU RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| 73S1210F-68M/F/PH | 功能描述:8位微控制器 -MCU RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| 73S1210F-68M/F/PJ | 制造商:Maxim Integrated Products 功能描述:SCR+PPAD/SRL INTFC/PWR MGT-3.11CODE - Rail/Tube |

| 73S1210F-68MR/F/PG | 功能描述:8位微控制器 -MCU RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。