- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360547 > 7LVC374APWDH (NXP SEMICONDUCTORS) Octal D-type flip-flop with 5-volt tolerant inputs/outputs; positive edge-trigger 3-State PDF資料下載

參數(shù)資料

| 型號(hào): | 7LVC374APWDH |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 通用總線功能 |

| 英文描述: | Octal D-type flip-flop with 5-volt tolerant inputs/outputs; positive edge-trigger 3-State |

| 中文描述: | LVC/LCX/Z SERIES, 8-BIT DRIVER, TRUE OUTPUT, PDSO20 |

| 文件頁(yè)數(shù): | 4/12頁(yè) |

| 文件大小: | 101K |

| 代理商: | 7LVC374APWDH |

Philips Semiconductors

Product specification

74LVC374A

Octal D-type flip-flop with 5-volt tolerant

inputs/outputs; positive edge-trigger (3-State)

1998 Jul 29

4

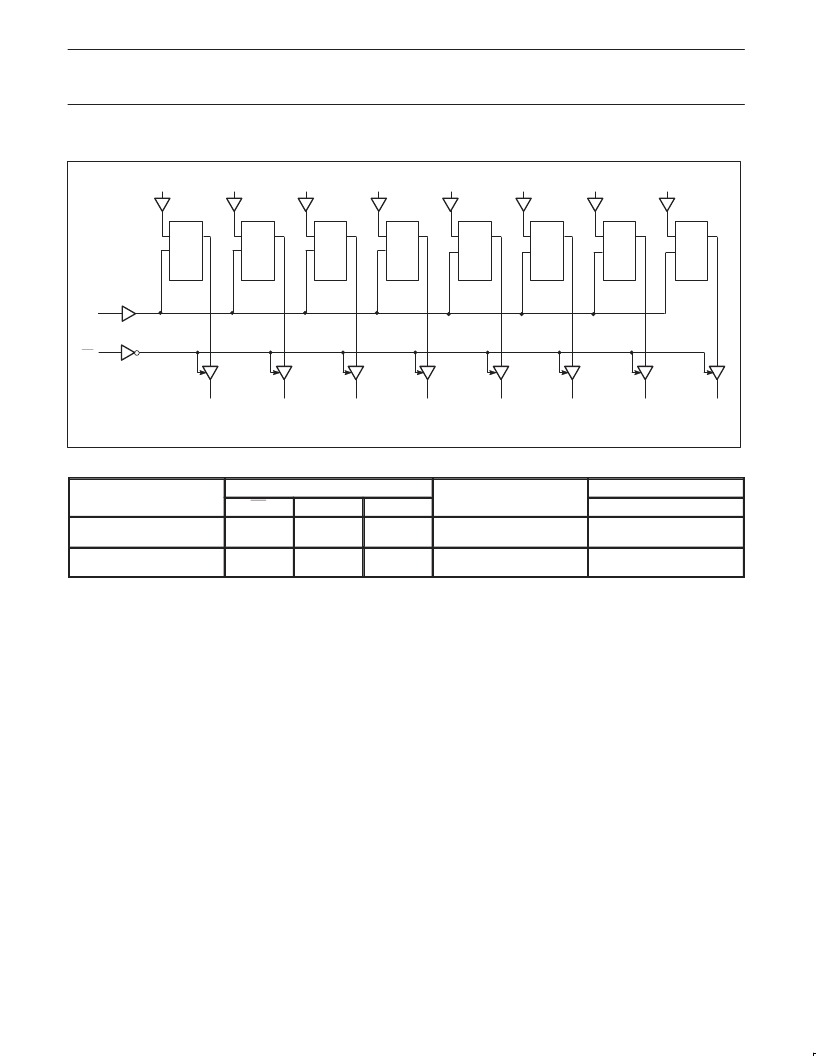

LOGIC DIAGRAM

Q

D

D0

Q0

D

D1

D

D2

D

D3

D

D4

D

D5

D

D6

D

D7

Q1

Q2

Q3

Q4

Q5

Q6

Q7

CP

OE

Q

Q

Q

Q

Q

Q

Q

SA00393

CP

CP

CP

CP

CP

CP

CP

CP

FF1

FF2

FF3

FF4

FF5

FF6

FF7

FF8

FUNCTION TABLE

OPERATING MODES

INPUTS

INTERNAL FLIP-FLOPS

OUTPUTS

OE

LE

D

n

l

h

Q

0

to Q

7

L

H

Load and read register

L

L

L

H

Load register and

disable outputs

H = HIGH voltage level

h

= HIGH voltage level one setup time prior to the LOW-to-HIGH CP transition

L

= LOW voltage level

l

= LOW voltage level one setup time prior to the LOW-to-HIGH CP transition

Z

= High impedance OFF-state

= LOW-to-HIGH clock transition

H

H

l

h

L

H

Z

Z

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 7LVC541APWDH | Octal buffer/line driver with 5-volt tolerant inputs/outputs 3-State |

| 7LVC543APWDH | Octal D-type registered transceiver 3-State |

| 7LVC544APWDH | Octal D-type registered transceiver, inverting 3-State |

| 7LVC573APWDH | Octal D-type transparent latch with 5-volt tolerant inputs/outputs 3-State |

| 7LVC574APWDH | Octal D-type flip-flop with 5-volt tolerant inputs/outputs; positive edge-trigger 3-State |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 7LVC541APWDH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Octal buffer/line driver with 5-volt tolerant inputs/outputs 3-State |

| 7LVC543APWDH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Octal D-type registered transceiver 3-State |

| 7LVC544APWDH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Octal D-type registered transceiver, inverting 3-State |

| 7LVC573APWDH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Octal D-type transparent latch with 5-volt tolerant inputs/outputs 3-State |

| 7LVC574APWDH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Octal D-type flip-flop with 5-volt tolerant inputs/outputs; positive edge-trigger 3-State |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。