- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378216 > 82572EI (INTEL CORP) Gigabit Ethernet Controller PDF資料下載

參數(shù)資料

| 型號: | 82572EI |

| 廠商: | INTEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Gigabit Ethernet Controller |

| 中文描述: | 1 CHANNEL(S), 1000M bps, LOCAL AREA NETWORK CONTROLLER, BGA256 |

| 封裝: | 17 X 17 MM, FC-BGA-256 |

| 文件頁數(shù): | 13/58頁 |

| 文件大小: | 318K |

| 代理商: | 82572EI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

Product Datasheet

7

82571EB/82572EI Gigabit Ethernet Controller

2.5

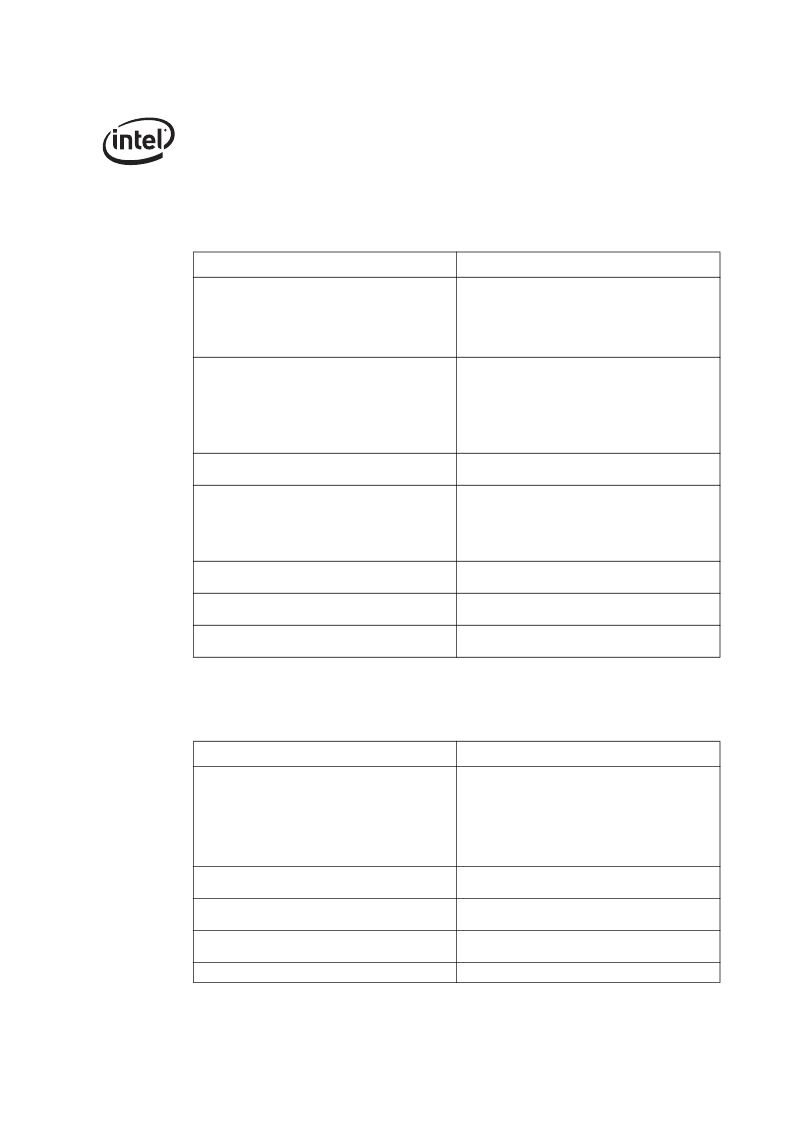

Manageability Features

2.6

Additional Device Features

Features

Benefits

Manageability features:

Two SMBus ports one with Fast Management Link

Capability

Alerting Standards Format 1.0 and 2.0

Advanced Power Management (Wake on LAN)

Alerting and control via standardized interfaces

Network management flexibility

Manageability data transfers up to 8 Mb/s peak rate

On-board microcontroller

Enables effective ASF 2.0 implementations

Promotes customized designs

Allows packets routing to and from either LAN port

and a server management processor

Supports serial text and keyboard redirection

Supports remote floppy/CD

Preboot eXecution Environment (PXE) Flash interface

support (32-bit nd 64-bit)

Local Flash interface for PXE image

Compliance with PCI Power Management 1.1 and ACPI

2.0 register set compliant including:

D0 and D3 power states

Network Device Class Power Management

Specification 1.1

PCI power management capability requirements for PC

and embedded applications

SNMP and RMON statistic counters

Easy system monitoring with industry standard

consoles

SDG 3.0, WfM 3.0, and PC2001 compliance

Remote network management capabilities through

DMI 2.0 and SNMP software

Wake on LAN support

Packet recognition and wake-up for NIC and LOM

applications without software configuration

Features

Benefits

82571EB: Two complete Gigabit Ethernet connections in a

single device

Inherent dual port teaming ability

High availability using one port for failover

Higher throughput than single Gigabit Ethernet port

Lower latency due to one electrical load on the bus

Saves critical board space

Reduced multi-port Gigabit Ethernet costs

Integrated SERDES

Supports backplane and fiber applications as well as

copper-based Gigabit

Four activity and link indication outputs (per port) that

directly drive LEDs

Link and activity indications (10, 100, and 1000 Mbps)

on each port

Programmable LED functionality

Software definable function (speed, link, and activity)

and blinking allowing flexible LED implementations

Internal PLL for clock generation can use a 25 MHz crystal

Lower component count and system cost

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 8257 | PROGRAMMABLE DMA CONTROLLER |

| 82586 | IEEE802.3 ETHERNET LAN COPROCESSOR |

| 82586-10 | IEEE802.3 ETHERNET LAN COPROCESSOR |

| 82586-6 | IEEE802.3 ETHERNET LAN COPROCESSOR |

| 82595FX | ISA BUS HIGH INTEGRATION ETHERNET CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 82573 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:GbE Controllers |

| 82-5730 | 制造商:TE Connectivity 功能描述: |

| 825732460 | 制造商:OMRON AUTOMATION AND SAFETY 功能描述:UM2460 UNIV MAT 5 M CBL TK1 SPEC |

| 82573-2460 | 制造商:OMRON AUTOMATION AND SAFETY 功能描述:UM2460 UNIV MAT 5 M CBL TK1 SPEC 制造商:OMRON INDUSTRIAL AUTOMATION 功能描述:UM5-2460-TK1 |

| 825732472 | 制造商:OMRON Industrial Automation 功能描述:UM2472 UNIV MAT 5 M CBL TK1 SPEC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。