- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378218 > 82C900 (SIEMENS AG) Standalone TwinCAN Controller(獨立 雙CAN控制器) PDF資料下載

參數(shù)資料

| 型號: | 82C900 |

| 廠商: | SIEMENS AG |

| 英文描述: | Standalone TwinCAN Controller(獨立 雙CAN控制器) |

| 中文描述: | 獨立TwinCAN控制器(獨立雙的CAN控制器) |

| 文件頁數(shù): | 15/29頁 |

| 文件大小: | 488K |

| 代理商: | 82C900 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁

82C900

Data Sheet

15

V 1.0D3, 2001-03

Preliminary

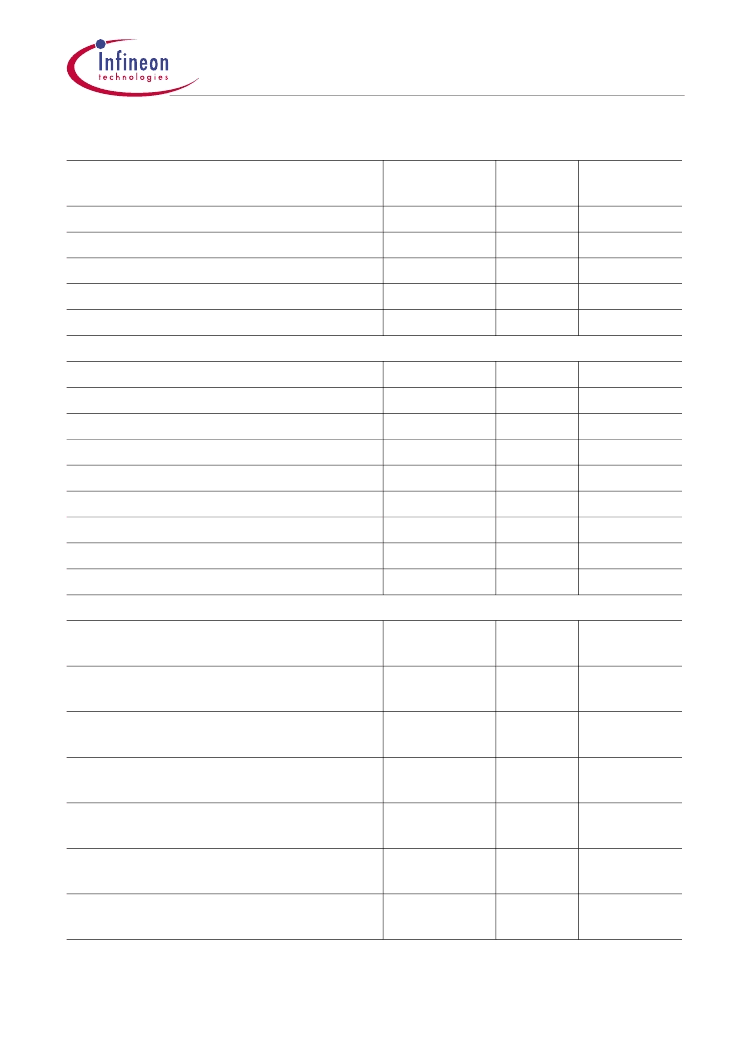

CAN Node A Global Int. Node Pointer Reg.

CAN Node A Frame Counter Register

CAN Node A INTID Mask Register 0

CAN Node A INTID Mask Register 4

CAN Node A Error Counter Register

TwinCAN Kernel, Node B Registers

CAN Node B Control Register

CAN Node B Status Register

CAN Node B Interrupt Pending Register

CAN Node B Bit Timing Register

CAN Node B Global Int. Node Pointer Reg.

CAN Node B Frame Counter Register

CAN Node B INTID Mask Register 0

CAN Node B INTID Mask Register 4

CAN Node B Error Counter Register

TwinCAN Kernel, Message Object Registers

CAN Message Object n Data Register 0

AGINP

AFCR

AIMR0

AIMR4

AECNT

0210

H

0214

H

0218

H

021C

H

0220

H

0000 0000

H

0000 0000

H

0000 0000

H

0000 0000

H

0060 0000

H

BCR

BSR

BIR

BBTR

BGINP

BFCR

BIMR0

BIMR4

BECNT

0240

H

0244

H

0248

H

024C

H

0250

H

0254

H

0258

H

025C

H

0260

H

0000 0001

H

0000 0000

H

0000 0000

H

0000 0000

H

0000 0000

H

0000 0000

H

0000 0000

H

0000 0000

H

0060 0000

H

MSGDRn0

0300

H

+ n*20

H

0304

H

+ n*20

H

0308

H

+ n*20

H

030C

H

+ n*20

H

0310

H

+ n*20

H

0314

H

+ n*20

H

0318

H

+ n*20

H

0000 0000

H

CAN Message Object n Data Register 4

MSGDRn4

0000 0000

H

CAN Message Object n Arbitration Register MSGARn

0000 0000

H

CAN Message Object n Acceptance Mask

Register

CAN Message Object n Message Control

Register

CAN Message Object n Message

Configuration Register

CAN Message Object n Gateway / FIFO

Control Register

MSGAMRn

FFFF FFFF

H

MSGCTRn

0000 5555

H

MSGCFGn

0000 0000

H

MSGFGCRn

0000 0000

H

1)

Registers with 32-bit reset values are located in the CAN RAM and have to be accessed accordingly. The

other registers are standard SFRs, which have 16-bit reset values.

Table 0-1

Register Name

Summary of Registers

(cont

’

d)

Register

Symbol

Address

Reset Value

1)

相關PDF資料 |

PDF描述 |

|---|---|

| 82CNQ030APBF | SCHOTTKY RECTIFIER 80 Amp New GenIII D-61 Package |

| 82CNQ030A | SCHOTTKY RECTIFIER |

| 82CNQ030ASL | SCHOTTKY RECTIFIER |

| 82CNQ030ASM | SCHOTTKY RECTIFIER |

| 82CNQ030SL | SCHOTTKY RECTIFIER 80 Amp |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 82C924 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| 82C925(100QFP) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Soundcard Circuits |

| 82C929 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| 82C930 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Soundcard Circuits |

| 82C931 | 制造商:OPTI 功能描述:SOUNDCARD CIRCUITS, 100 Pin, Plastic, QFP 制造商:Opti Inc 功能描述:SOUNDCARD CIRCUITS, 100 Pin, Plastic, QFP |

發(fā)布緊急采購,3分鐘左右您將得到回復。