- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24776 > 935063300112 (NXP SEMICONDUCTORS) LV/LV-A/LVX/H SERIES, DUAL POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PDSO14 PDF資料下載

參數(shù)資料

| 型號: | 935063300112 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 鎖存器 |

| 英文描述: | LV/LV-A/LVX/H SERIES, DUAL POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PDSO14 |

| 封裝: | 3.90 MM, PLASTIC, MS-012AB, SOT-109-1, SO-14 |

| 文件頁數(shù): | 11/12頁 |

| 文件大小: | 135K |

| 代理商: | 935063300112 |

1999 Aug 05

8

Philips Semiconductors

Product specication

16-bit D-type transparent latch with 30

series

termination resistors; 5 V input/output tolerant; 3-state

74LVC162373A;

74LVCH162373A

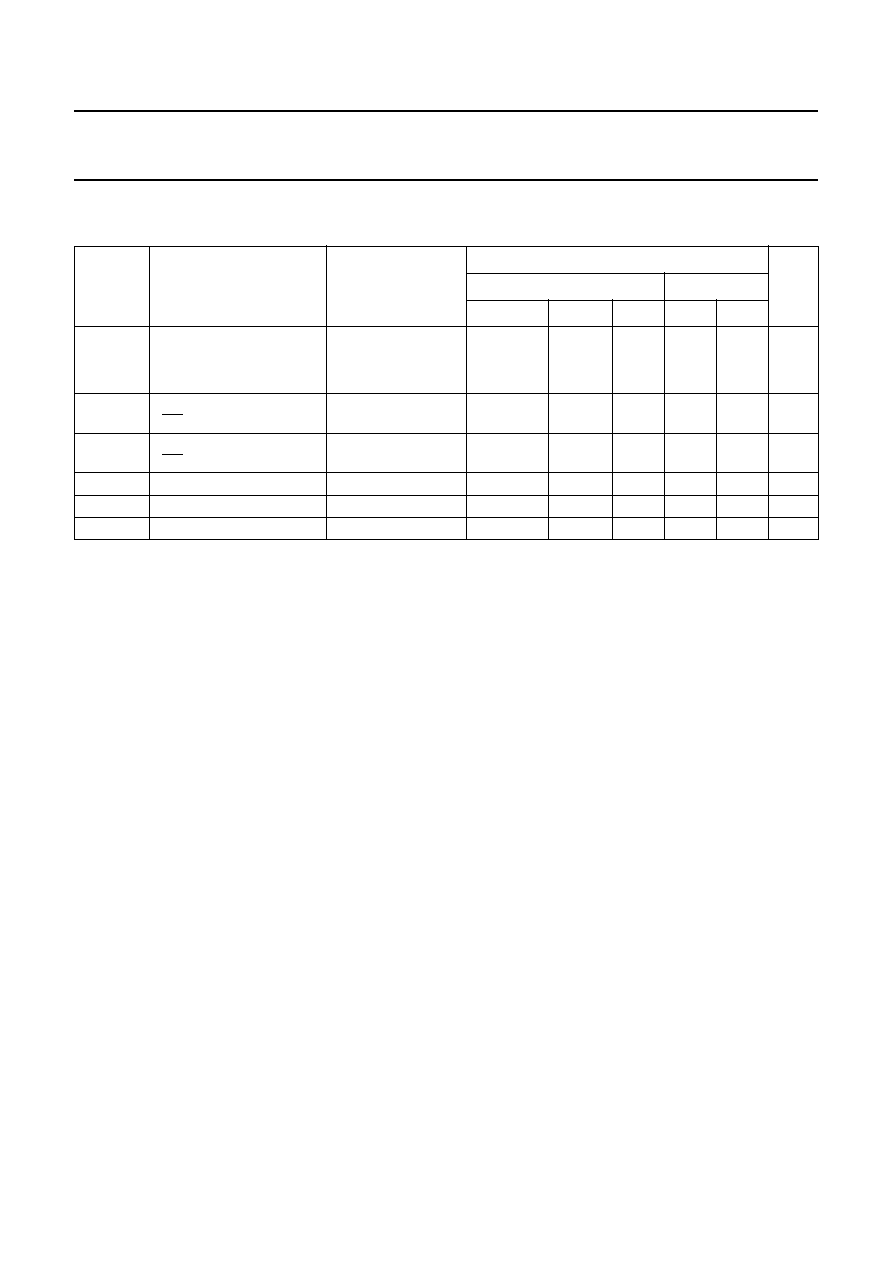

AC CHARACTERISTICS

GND = 0 V; tr =tf ≤ 2.5 ns; Tamb = 40 to +85 °C.

Note

1. Typical values at VCC = 3.3 V and Tamb =25 °C.

SYMBOL

PARAMETER

WAVEFORMS

LIMITS

UNIT

VCC = 3.3 V ±0.3 V

VCC = 2.7 V

MIN.

TYP.(1)

MAX.

MIN.

MAX.

tPHL/tPLH

propagation delay

nDn to nQn

see Figs 6 and 10

1.5

3.3

5.4

1.5

6.4

ns

nLE to nQn

see Figs 7 and 10

1.5

3.5

5.8

1.5

6.8

ns

tPZH/tPZL

3-state output enable time

nOE to nQn

see Figs 9 and 10

1.5

4.0

7.3

1.5

8.3

ns

tPHZ/tPLZ

3-state output disable time

nOE to nQn

see Figs 9 and 10

1.5

3.4

4.8

1.5

5.8

ns

tW

nLE pulse width HIGH

see Fig.7

4.0

2.0

3

ns

tsu

set-up time nDn to nLE

see Fig.8

+2.0

0.1

1.7

ns

th

hold time nDn to nLE

see Fig.8

1.5

0.1

1.2

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935170210112 | LV/LV-A/LVX/H SERIES, DUAL POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PDSO14 |

| 935063300118 | LV/LV-A/LVX/H SERIES, DUAL POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PDSO14 |

| 935171060118 | LVT SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO20 |

| 935176350118 | LVT SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO20 |

| 935176350112 | LVT SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935066270112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY I.C. |

| 93506EM8 | 制造商:undefined 功能描述: |

| 935079-000 | 制造商:TE Connectivity 功能描述:55A1841-16-MST4-9CS2275 - Cable Rools/Shrink Tubing |

| 935087-000 | 制造商:TE Connectivity 功能描述:301A511-51-05/164-0 - Bulk |

| 935087N001 | 制造商:TE Connectivity 功能描述:301A511-51-05/164-CS7092 制造商:TE Connectivity 功能描述:301A511-51-05/164-CS7092 - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。