- 您現(xiàn)在的位置:買賣IC網 > PDF目錄36334 > 935260018557 (NXP SEMICONDUCTORS) SPECIALTY CONSUMER CIRCUIT, PQFP64 PDF資料下載

參數資料

| 型號: | 935260018557 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| 封裝: | PLASTIC, SOT-393, QFP-64 |

| 文件頁數: | 53/75頁 |

| 文件大?。?/td> | 479K |

| 代理商: | 935260018557 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁當前第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁

1998 May 15

57

Philips Semiconductors

Product specication

Enhanced Video Input Processor (EVIP)

SAA7111A

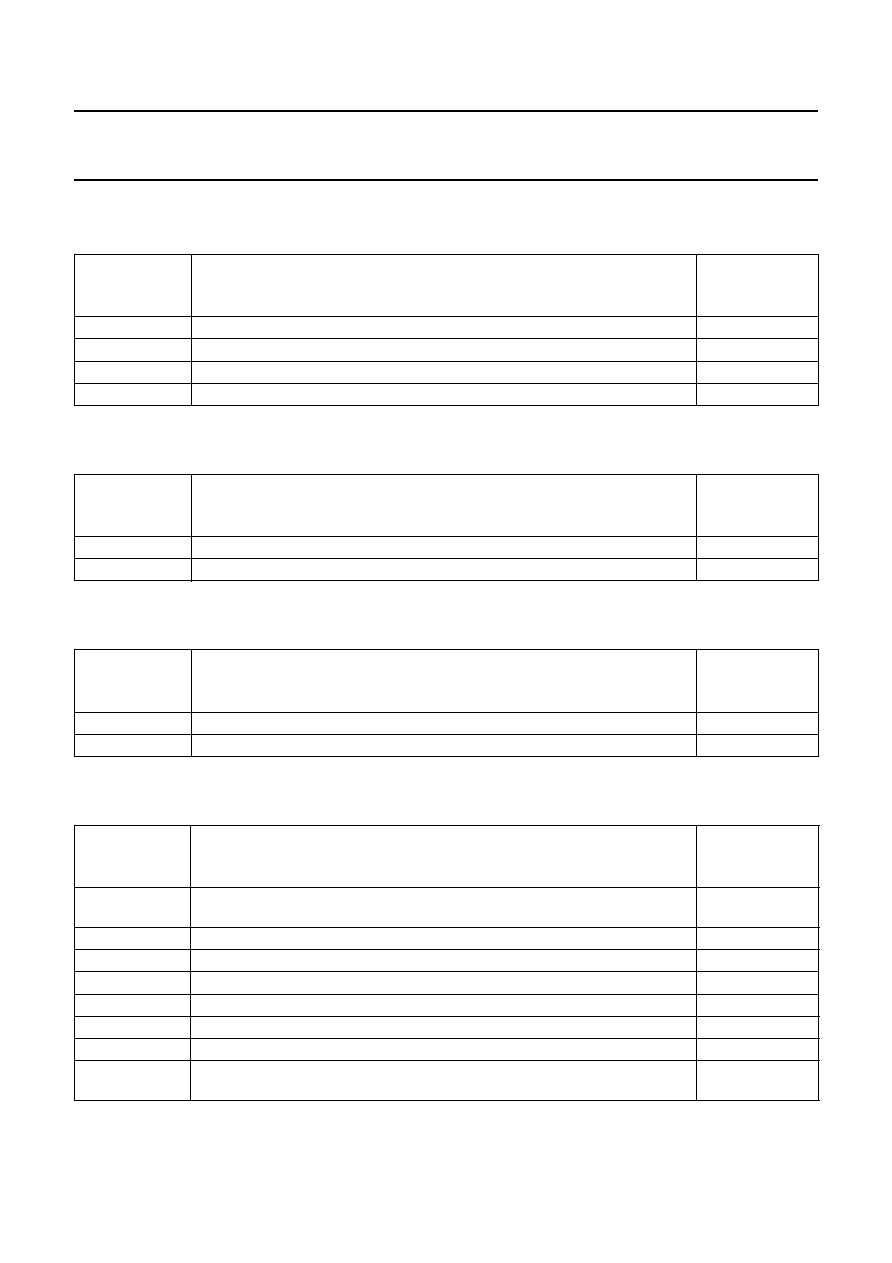

17.2.22 SUBADDRESS 1A (READ-ONLY REGISTER)

Table 37 Line-21 text slicer status SA 1A, D3 to D0

17.2.23 SUBADDRESS 1B (READ-ONLY REGISTER)

Table 38 First decoded data byte of the text slicer SA 1B

17.2.24 SUBADDRESS 1C (READ-ONLY REGISTER)

Table 39 Second decoded data byte of the text slicer SA 1C

17.2.25 SUBADDRESS 1F (READ-ONLY REGISTER)

Table 40 Status byte SA 1F

I2C-BUS

STATUS BIT

NAME

FUNCTION

STATUS BIT

F1RDY

new data on eld 1 has been acquired (for asynchronous reading); active HIGH

D0

F1VAL

line-21 of eld 1 carries valid data; active HIGH

D1

F2RDY

new data on eld 2 has been acquired (for asynchronous reading); active HIGH

D2

F2VAL

line-21 of eld 2 carries valid data; active HIGH

D3

I2C-BUS

TEXT DATA

BITS

FUNCTION

DATA BITS

BYTE1 (6 to 0)

data bit 6 to 0 of rst data byte

D6 to D0

P1

parity error ag bit; bit goes HIGH when a parity error has occurred

D7

I2C-BUS

TEXT DATA

BITS

FUNCTION

DATA BITS

BYTE2 (6 to 0)

data bit 6 to 0 of second data byte

D6 to D0

P2

parity error ag bit; bit goes HIGH when a parity error has occurred

D7

I2C-BUS

STATUS BIT

NAME

FUNCTION

STATUS BIT

CODE

colour signal in accordance with selected standard has been detected; active

HIGH

D0

SLTCA

slow time constant active in WIPA-mode; active HIGH

D1

WIPA

white peak loop is activated; active HIGH

D2

GLIMB

gain value for active luminance channel is limited [min (bottom)]; active HIGH

D3

GLIMT

gain value for active luminance channel is limited [max (top)]; active HIGH

D4

FIDT

identication bit for detected eld frequency; LOW = 50 Hz, HIGH = 60 Hz

D5

HLCK

status bit for locked horizontal frequency; LOW = locked, HIGH = unlocked

D6

STTC

status bit for horizontal phase loop; LOW = TV time-constant,

HIGH = VTR time-constant

D7

相關PDF資料 |

PDF描述 |

|---|---|

| 935263652557 | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| 935233400112 | SPECIALTY CONSUMER CIRCUIT, PDIP24 |

| 935233410112 | SPECIALTY CONSUMER CIRCUIT, PDSO24 |

| 935233410118 | SPECIALTY CONSUMER CIRCUIT, PDSO24 |

| 935233410518 | SPECIALTY CONSUMER CIRCUIT, PDSO24 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 935260093112 | 制造商:NXP Semiconductors 功能描述:IC AVIC ADV BASESTATION 14SOIC |

| 935261069122 | 制造商:NXP Semiconductors 功能描述:IC SECURITY TRANSPONDER PLLMC |

| 935262025112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935262217118 | 制造商:NXP Semiconductors 功能描述:Real Time Clock Serial 8-Pin SO T/R |

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

發(fā)布緊急采購,3分鐘左右您將得到回復。