- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24826 > 935263206557 (NXP SEMICONDUCTORS) 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP80 PDF資料下載

參數(shù)資料

| 型號: | 935263206557 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP80 |

| 封裝: | PLASTIC, QFP-80 |

| 文件頁數(shù): | 24/76頁 |

| 文件大?。?/td> | 567K |

| 代理商: | 935263206557 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

Philips Semiconductors

Product specification

P83C557E4/P80C557E4/P89C557E4

Single-chip 8-bit microcontroller

1999 Mar 02

30

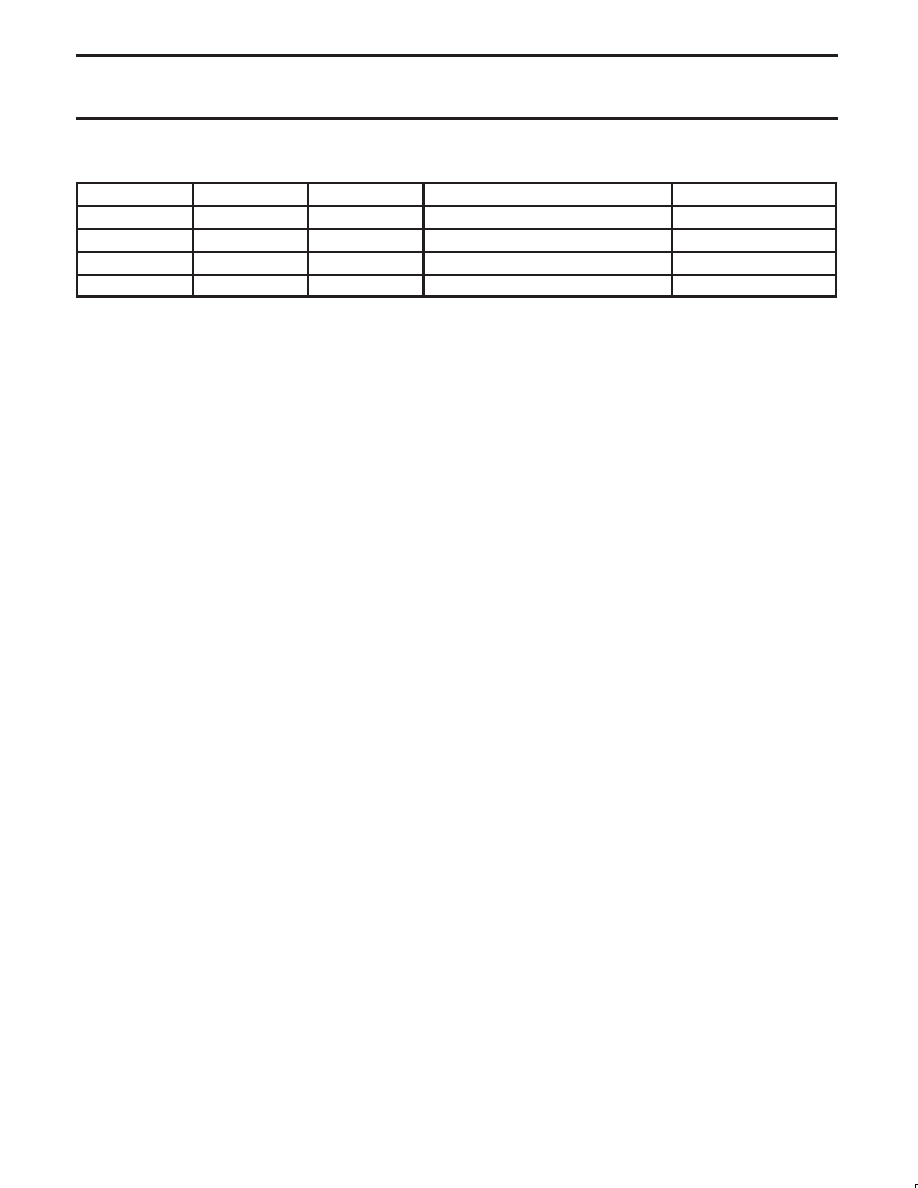

Table 23.

Description of S0CON bits

SM0

SM1

MODE

DESCRIPTION

BAUD RATE

0

Shift register

fCLK/12

0

1

8-bit UART

variable

1

0

2

9-bit UART

fCLK/64 or fCLK/32

1

3

9-bit UART

variable

6.9.2

SIO1 (I2C-bus Interface)

The SIO1 of the P8xC557E4 provides the fast-mode, which allows a

fourthfold increase of the bitrate up to 400 kHz. Nevertheless it is

downward compatible, i.e. it can be used in a 0 to 100 Kbit/s I2C bus

system.

Except from the bit rate selection (see Table 25) and the timing of

the SCL and SDA signals (see AC electrical characteristics in

section 11) the SIO circuit is the same as described in detail in the

80C51 Data Handbook IC20 for the 8xC552 microcontroller.

The I2C-bus is a simple bidirectional 2-wire bus for efficient inter-IC

data exchange. Features of the I2C-bus are:

Only two bus lines are required: a serial clock line (SCL) and a

serial data line (SDA)

Each device connected to the bus is software addressable by a

unique address

Masters can operate as Master-transmitter or as Master-receiver

It’s a true multi-master bus including collision detection and

arbitration to prevent data corruption if two or more masters

simultaneously initiate data transfer

Serial clock synchronization allows devices with different bit rates

to communicate via the same serial bus

ICs can be added to or removed from an I2C-bus system without

affecting any other circuit on the bus

Fault diagnostics and debugging are simple; malfunctions can be

immediately traced

For more information on the I2C-bus specification (including

fast-mode) please refer to the Philips publication number 9398 393

40011 and/or the 80C51 Data Handbook IC20.

The on-chip I2C logic provides a serial interface that meets the

I2C-bus specification, supporting all I2C-bus modes of operation,

they are:

Master transmitter

Master receiver

Slave transmitter

Slave receiver

The SI01 logic performs a byte oriented data transport, clock

generation, address recognition and bus control arbitration are all

controlled by hardware. Via two pins the external I2C-bus is

interfaced to the SIO1 logic:

SCL serial clock I/O and SDA serial data I/O, (see Special Function

Register bit S1CON.6/ENS1 for enabling the SIO1 logic).

The SIO1 logic handles byte transfer autonomously. It keeps track of

the serial transfers, and a status register (S1STA) reflects the status

of SIO1 and the I2C-bus.

Via the following four Special Function Registers the CPU interfaces

to the I2C logic.

S1CON

control register. Bit addressable by the CPU

S1STA

status register whose contents may be used as a

vector to service routines.

S1DAT

data shift register. The data byte is stable as long

as S1CON.3/SI=1.

S1ADR

slave address register. It’s LSB enables/ disables

general call address recognition.

相關PDF資料 |

PDF描述 |

|---|---|

| 935268065557 | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP80 |

| 935263263557 | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP80 |

| 935263262557 | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP80 |

| 935263208557 | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP80 |

| 935263156518 | 8-BIT, FLASH, 16 MHz, MICROCONTROLLER, PQFP80 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

發(fā)布緊急采購,3分鐘左右您將得到回復。