- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25516 > 954204AGLFT (INTEGRATED DEVICE TECHNOLOGY INC) 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF資料下載

參數(shù)資料

| 型號: | 954204AGLFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘產(chǎn)生/分配 |

| 英文描述: | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封裝: | 6.10 MM, 0.50 MM PITCH, GREEN, MO-153, TSSOP-56 |

| 文件頁數(shù): | 1/20頁 |

| 文件大?。?/td> | 261K |

| 代理商: | 954204AGLFT |

Integrated

Circuit

Systems, Inc.

ICS954204

0933D—03/16/05

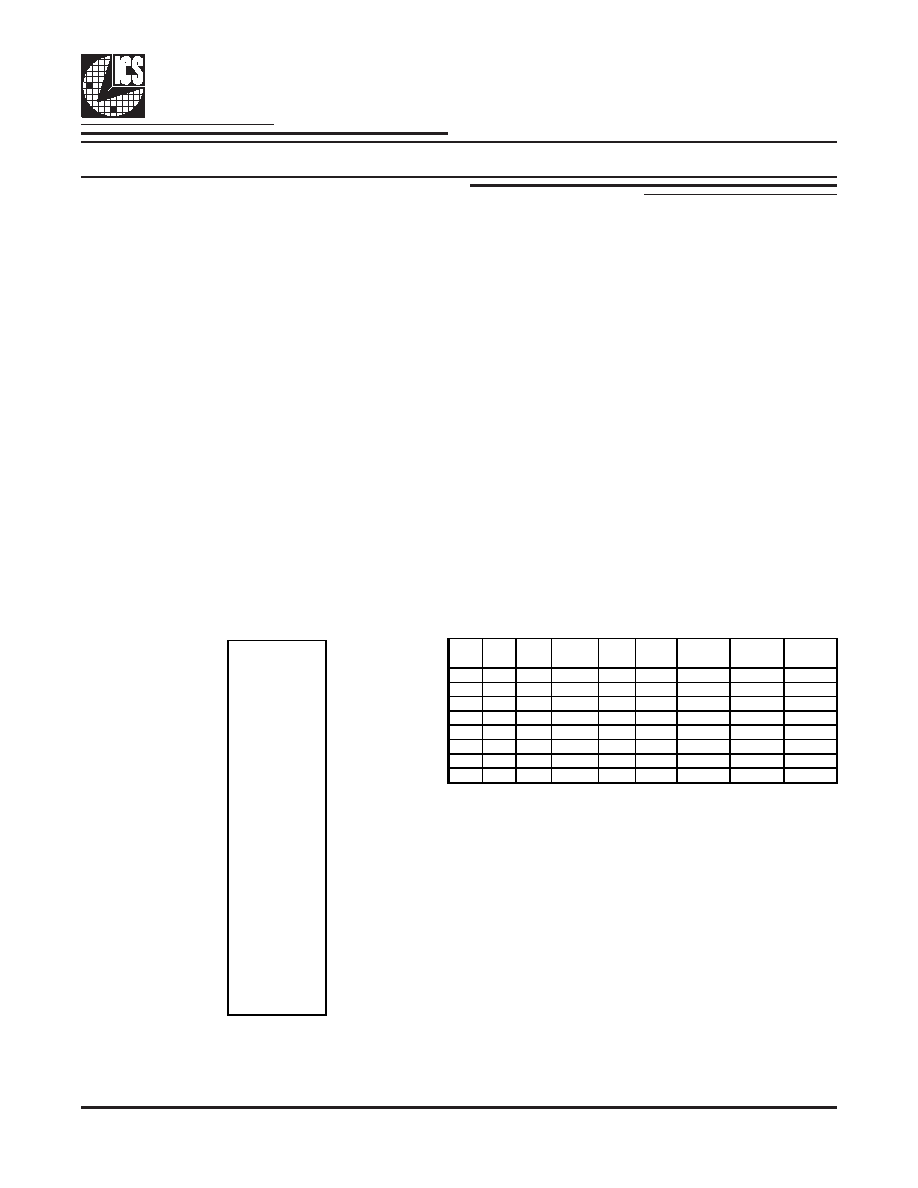

Pin Configuration

Recommended Application:

CK410M Compliant Main Clock with Integrated LCD Spread

Spectrum Clock.

Output Features:

2 - 0.7V current-mode differential CPU pairs

5 - 0.7V current-mode differential SRC pair for SATA and

PCI-E

1 - 0.7V current-mode differential CPU/SRC selectable

pair

4 - PCI (33MHz)

2 - PCICLK_F, (33MHz) free-running

1 - USB, 48MHz

1 - DOT, 96MHz, 0.7V current differential pair

1 - REF, 14.318MHz

1 - 0.7V current-mode differential LCD/SRC selectable

pair.

Key Specifications:

CPU outputs cycle-cycle jitter < 85ps

SRC outputs cycle-cycle jitter < 125ps

Programmable Timing Control Hub for Mobile P4 Systems

Functionality

PCI outputs cycle-cycle jitter < 500ps

+/- 300ppm frequency accuracy on CPU & SRC clocks

+/- 100ppm frequency accuracy on USB clocks

Features/Benefits:

Supports tight ppm accuracy clocks for Serial-ATA and

SRC

Supports programmable spread percentage and

frequency

Uses external 14.318MHz crystal, external crystal load

caps are required for frequency tuning

Supports undriven differential CPU, SRC pair in PD#

for power management.

CLKREQ pins to support SRC power management.

VDDPCI

156 PCICLK2

GND

255 PCI/SRC_STOP#

PCICLK3

354 CPU_STOP#

PCICLK4

453 FSLC/TEST_SEL

PCICLK5

552 REFOUT

GND

651 GND

VDDPCI

750 X1

ITP_EN/PCICLK_F0

849 X2

*SELSRC_LCDCLK#/PCICLK_F1

948 VDDREF

Vtt_PwrGd#/PD

10

47 SDATA

VDD48

11

46 SCLK

FSLA/USB_48MHz 12

45 GND

GND

13

44 CPUCLKT0

DOTT_96MHz

14

43 CPUCLKC0

DOTC_96MHz

15

42 VDDCPU

FSLB/TEST_MODE 16

41 CPUCLKT1

LCDCLK_SST/SRCCLKT0

17

40 CPUCLKC1

LCDCLK_SSC/SRCCLKC0

18

39 IREF

SRCCLKT1

19

38 GNDA

SRCCLKC1

20

37 VDDA

VDDSRC

21

36 CPUCLKT2_ITP/SRCCLKT7

SRCCLKT2

22

35 CPUCLKC2_ITP/SRCCLKC7

SRCCLKC2

23

34 VDDSRC

SRCCLKT3

24

33 CLKREQA#*

SRCCLKC3

25

32 CLKREQB#*

SRCCLKT4_SATA

26

31 SRCCLKT5

SRCCLKC4_SATA

27

30 SRCCLKC5

VDDSRC

28

29 GND

56-pin TSSOP

*100Kohm Pull-Up Resistor

IC

S

9

5

4204

FS_C FS_B FS_A

CPU

MHz

SRC

MHz

PCI

MHz

REF

MHz

USB

MHz

DOT

MHz

0

266.67 100.00 33.33

14.318

48.00

96.00

0

1

133.33 100.00 33.33

14.318

48.00

96.00

0

1

0

200.00 100.00 33.33

14.318

48.00

96.00

0

1

166.67 100.00 33.33

14.318

48.00

96.00

1

0

333.33 100.00 33.33

14.318

48.00

96.00

1

0

1

100.00 100.00 33.33

14.318

48.00

96.00

1

0

400.00 100.00 33.33

14.318

48.00

96.00

1

200.00 100.00 33.33

14.318

48.00

96.00

1.

2. FS_B and FS_A are low-threshold inputs. Please see the VIL_FS and VIH_FS

specifications in the Input/Supply/Common Output Parameters Table for

correct values.

FS_C is a three-level input. Please see VIL_FS and VIH_FS specifications in the

Input/Supply/Common Output Parameters Table for correct values. Also refer

to the Test Clarification Table.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 954204AGT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 954206BGT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 954206BFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 954206BFLFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 9552-6006-01 | RF/MICROWAVE FIXED ATTENUATOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 954204BGLF | 制造商:Integrated Device Technology Inc 功能描述:56 TSSOP (LEAD FREE) - Rail/Tube |

| 954204BGLN | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Synthesizer Dual 56-Pin TSSOP Tube |

| 954204BGLNT | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Synthesizer Dual 56-Pin TSSOP T/R |

| 954204CGLF | 功能描述:時鐘合成器/抖動清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 954204CGLFT | 功能描述:時鐘合成器/抖動清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。