- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25564 > 9DB401CGLFT (INTEGRATED DEVICE TECHNOLOGY INC) 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 PDF資料下載

參數(shù)資料

| 型號(hào): | 9DB401CGLFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時(shí)鐘及定時(shí) |

| 英文描述: | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 封裝: | 4.40 MM, 0.65 MM PITCH, ROHS COMPLIANT, MO-153, TSSOP-28 |

| 文件頁(yè)數(shù): | 4/17頁(yè) |

| 文件大小: | 160K |

| 代理商: | 9DB401CGLFT |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)

IDT

Four Output Differential Buffer for PCI Express

9DB401C

REV H 01/27/11

9DB401C

Four Output Differential Buffer for PCI Express

12

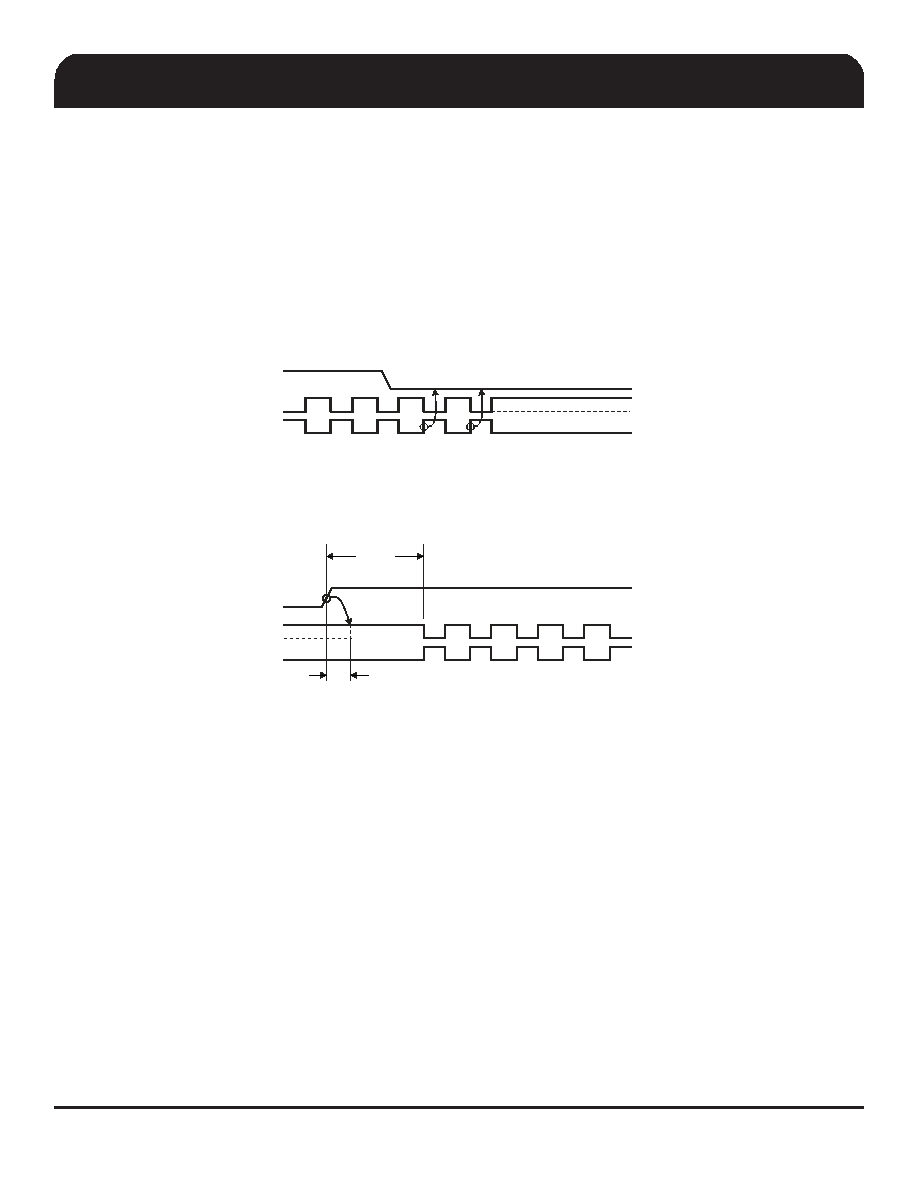

The PD# pin cleanly shuts off all clocks and places the device into a power saving mode. PD# must be asserted before shutting

off the input clock or power to insure an orderly shutdown. PD is asynchronous active-low input for both powering down the

device and powering up the device. When PD# is asserted, all clocks will be driven high, or tri-stated (depending on the PD#

drive mode and Output control bits) before the PLL is shut down.

PD#

When PD# is sampled low by two consecutive rising edges of DIF#, all DIF outputs must be held High, or tri-stated (depending

on the PD# drive mode and Output control bits) on the next High-Low transition of the DIF# outputs. When the PD# drive mode

bit is set to ‘0’, all clock outputs will be held with DIF driven High with 2 x IREF and DIF# tri-stated. If the PD# drive mode bit is

set to ‘1’, both DIF and DIF# are tri-stated.

PD# Assertion

Power-up latency is less than 1 ms. This is the time from de-assertion of the PD# pin, or VDD reaching 3.3V, or the time from

valid SRC_IN clocks until the time that stable clocks are output from the device (PLL Locked). If the PD# drive mode bit is set

to ‘1’, all the DIF outputs must driven to a voltage of >200 mV within 300 ms of PD# de-assertion.

PD# De-assertion

PWRDWN#

DIF

DIF#

PWRDWN#

DIF

DIF#

Tstable

<1mS

Tdrive_PwrDwn#

<300uS, >200mV

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 9DB401CFLF | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB403DGILFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB403DFILFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB403DFILF | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB403DGLF | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9DB403DFILF | 功能描述:時(shí)鐘緩沖器 4 OUTPUT PCIE GEN1 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB403DFILFT | 功能描述:時(shí)鐘緩沖器 4 OUTPUT PCIE GEN1 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB403DFLF | 功能描述:時(shí)鐘緩沖器 4 OUTPUT PCIE GEN1 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB403DFLFT | 功能描述:時(shí)鐘緩沖器 4 OUTPUT PCIE GEN1 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB403DGILF | 功能描述:時(shí)鐘緩沖器 4 OUTPUT PCIE GEN1 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。