- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄294787 > A32400DX-1BG313I FPGA, 2526 CLBS, 40000 GATES, PBGA313 PDF資料下載

參數(shù)資料

| 型號: | A32400DX-1BG313I |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 2526 CLBS, 40000 GATES, PBGA313 |

| 封裝: | BGA-313 |

| 文件頁數(shù): | 19/22頁 |

| 文件大小: | 217K |

| 代理商: | A32400DX-1BG313I |

6

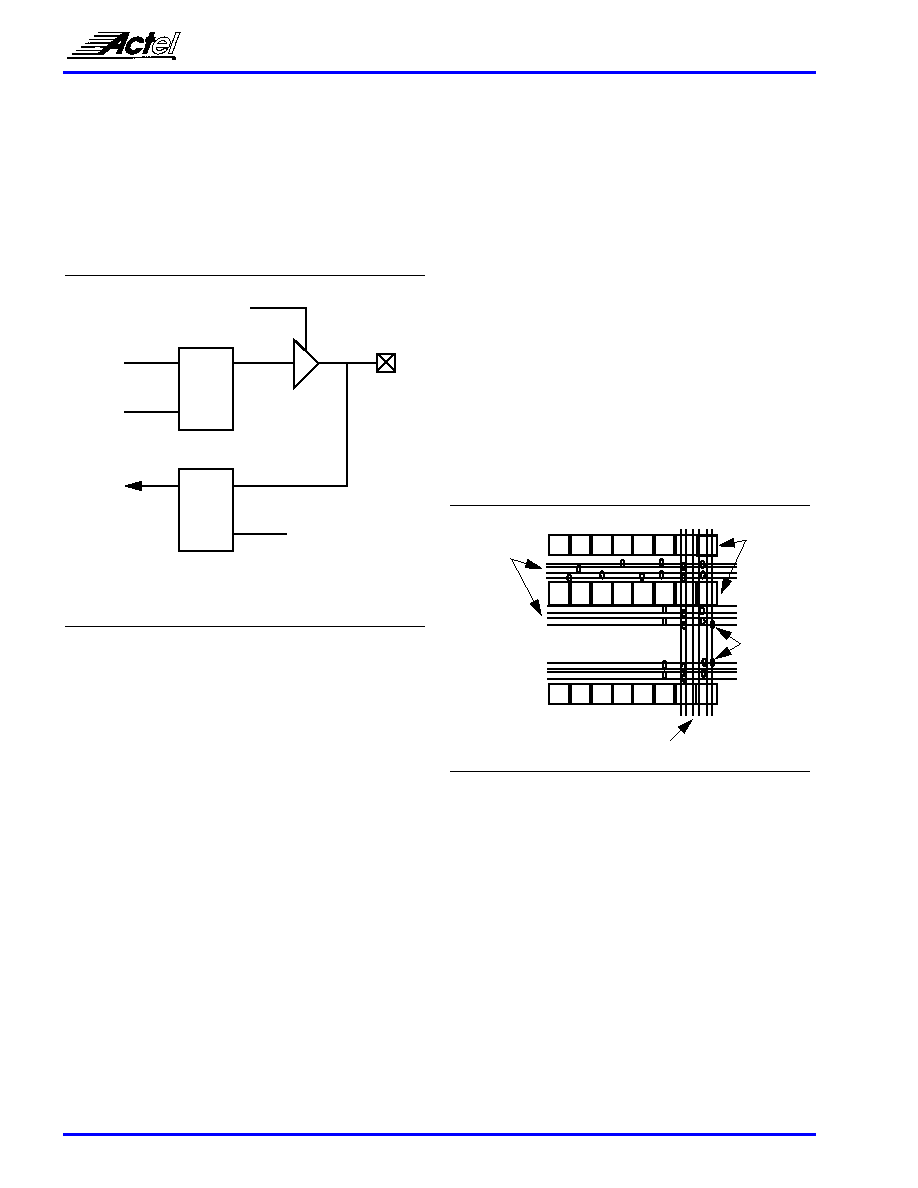

I/O Modules

The I/O modules provide the interface between the device

pins and the logic array (shown in Figure 5). A variety of I/O

configurations, determined by a library macro selection, can

be implemented in the module (refer to the Macro Library

Guide for more information). I/O modules contain input and

output latches as well as a tri-state buffer. These features

allow the module to be configured for input, output, or

bi-directional pins.

I/O modules contain input and output latches for capturing

data prior to and/or from the device pins. In addition, the

Actel Designer Series software tools can build a D flip-flop

using a C-module in conjunction with the I/O latch to register

input and/or output signals. Actel’s Designer Series

development tools provide a design library of I/O macros

which can implement all I/O configurations supported by the

3200DX.

Routing Structure

The 3200DX architecture uses Horizontal and Vertical

routing tracks to interconnect the various logic and I/O

modules. These routing tracks are metal interconnects that

may either be of continuous length or broken into pieces

called segments. Varying segment lengths allows the

interconnect of over 90% of design tracks to occur with only

two antifuse connections. Segments can be joined together at

the ends, using antifuses, to increase their lengths up to the

full

length

of

the

track.

All

interconnects

can

be

accomplished with a maximum of four antifuses.

Horizontal Routing

Horizontal channels are located between the rows of modules

and are composed of several routing tracks. The horizontal

routing tracks within the channel are divided into one or more

segments. The minimum horizontal segment length is the

width of a module-pair, and the maximum horizontal

segment length is the full length of the channel. Any segment

that spans more than one-third the row length is considered a

long horizontal segment. A typical channel is shown in

Figure 6. Non-dedicated horizontal routing tracks are used to

route signal nets. Dedicated routing tracks are used for the

global clock networks and for power and ground tie-off

tracks.

Vertical Routing

Other tracks run vertically through the module. Vertical

tracks are of three types: input, output, and long. Vertical

tracks are also divided into one or more segments. Each

segment in an input track is dedicated to the input of a

particular module. Each segment in an output track is

dedicated to the output of a particular module. Long segments

are uncommitted and can be assigned during routing. Each

output segment spans four channels (two above and two

below), except near the top and bottom of the array where

edge effects occur. An example of vertical routing tracks and

segments is shown in Figure 6.

Antifuse Structures

An antifuse is a “normally open” structure as opposed to the

normally closed fuse structure used in PROMs or PALs. The

use of antifuses to implement a Programmable Logic Device

results in highly testable structures as well as efficient

programming algorithms. The structure is highly testable

because there are no pre-existing connections; therefore,

temporary connections can be made using pass transistors.

These temporary connections can isolate individual antifuses

to be programmed as well as isolate individual circuit

structures to be tested. This can be done both before and after

programming. For example, all metal tracks can be tested for

continuity and shorts between adjacent tracks, and the

functionality of all logic modules can be verified.

Figure 5 I/O Module

G/CLK*

QD

EN

PAD

* Can be congured as a Latch or D Flip-Flop

From Array

To Array

(using C-module)

G/CLK*

QD

Figure 6 Horizontal Routing Tracks and Segments

Vertical routing tracks

Antifuses

Logic

Segmented

horizontal

routing

tracks

Modules

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A32400DX-1PQ240C | FPGA, 2526 CLBS, 40000 GATES, PQFP240 |

| A32400DX-1PQ240I | FPGA, 2526 CLBS, 40000 GATES, PQFP240 |

| A32400DX-2BG313C | FPGA, 2526 CLBS, 40000 GATES, PBGA313 |

| A32400DX-2BG313I | FPGA, 2526 CLBS, 40000 GATES, PBGA313 |

| A32400DX-2PQ240C | FPGA, 2526 CLBS, 40000 GATES, PQFP240 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A32400DX-1RQ240C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| A32400DX-1RQ240I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| A32400DX-2RQ240C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| A32400DX-2RQ240I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| A32400DX-3RQ240C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。