- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄298744 > A42MX24-2TQ100 (Electronic Theatre Controls, Inc.) 40MX and 42MX FPGA Families PDF資料下載

參數(shù)資料

| 型號: | A42MX24-2TQ100 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 40MX and 42MX FPGA Families |

| 中文描述: | 40MX和42MX FPGA系列 |

| 文件頁數(shù): | 21/93頁 |

| 文件大小: | 854K |

| 代理商: | A42MX24-2TQ100 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁

28

Data Device Corporation

www.ddc-web.com

BU-6474X/6484X/6486X

J-07/05-0

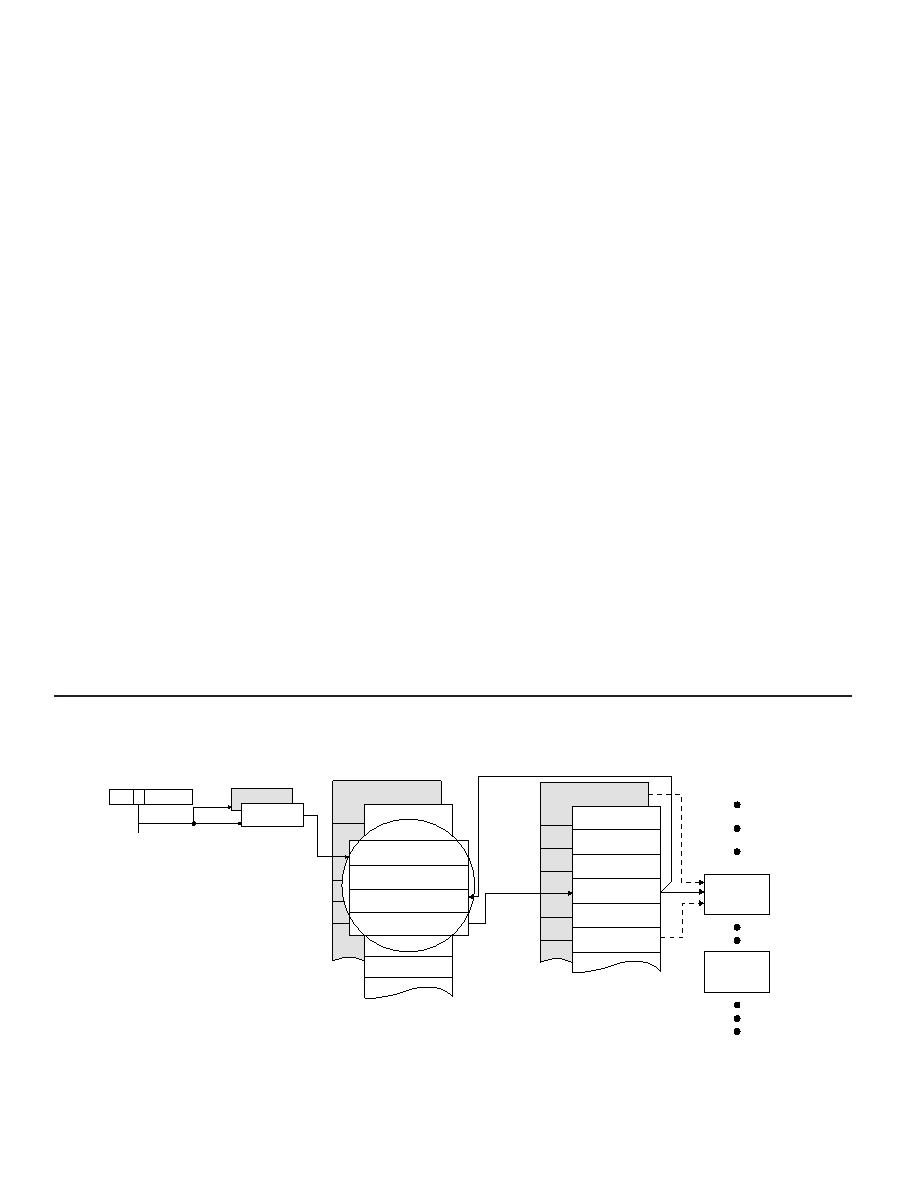

SINGLE BUFFERED MODE

The operation of the single buffered RT mode is illustrated in

FIGURE 6. In the single buffered mode, the respective lookup

table entry must be written by the host processor. Received data

words are written to, or transmitted data words are read from the

data word block with starting address referenced by the lookup

table pointer. In the single buffered mode, the current lookup

table pointer is not updated by the Mini-ACE Mark3 memory

management logic. Therefore, if a subsequent message is

received for the same subaddress, the same Data Word block

will be overwritten or overread.

SUBADDRESS DOUBLE BUFFERING MODE

The Mini-ACE Mark3 provides a double buffering mechanism for

received data, that may be selected on an individual subaddress

basis for any or all receive (and/or broadcast) subaddresses. This

is illustrated in FIGURE 7. It should be noted that the Subaddress

Double Buffering mode is applicable for receive data only, not for

transmit data. Double buffering of transmit messages may be

easily implemented by software techniques.

The purpose of the subaddress double buffering mode is to pro-

vide data sample consistency to the host processor. This is

accomplished by allocating two 32-word data word blocks for each

individual receive (and/or broadcast receive) subaddress. At any

given time, one of the blocks will be designated as the "active"

1553 block while the other will be considered as "inactive". The

data words for the next receive command to that subaddress will

be stored in the active block. Following receipt of a valid message,

the Mini-ACE Mark3 will automatically switch the active and inac-

tive blocks for that subaddress. As a result, the latest, valid, com-

plete data block is always accessible to the host processor.

CIRCULAR BUFFER MODE

The operation of the Mini-ACE Mark3's circular buffer RT mem-

ory management mode is illustrated in FIGURE 8. As in the sin-

gle buffered and double buffered modes, the individual lookup

table entries are initially loaded by the host processor. At the

start of each message, the lookup table entry is stored in the

third position of the respective message block descriptor in the

descriptor stack area of RAM. Receive or transmit data words

are transferred to (from) the circular buffer, starting at the loca-

tion referenced by the lookup table pointer.

In general, the location after the last data word written or read

(modulo the circular buffer size) during the message is written to

the respective lookup table location during the end-of-message

sequence. By so doing, data for the next message for the respec-

tive transmit, receive(/broadcast), or broadcast subaddress will

be accessed from the next lower contiguous block of locations in

the circular buffer.

For the case of a receive (or broadcast receive) message with a

data word error, there is an option such that the lookup table

pointer will only be updated following receipt of a valid message.

That is, the pointer will not be updated following receipt of a

message with an error in a data word. This allows failed mes-

sages in a bulk data transfer to be retried without disrupting the

circular buffer data structure, and without intervention by the

RT's host processor.

GLOBAL CIRCULAR BUFFER

Beyond the programmable choice of single buffer mode, double

buffer mode, or circular buffer mode, programmable on an individ-

ual subaddress basis, the Mini-ACE Mark3 RT architecture pro-

FIGURE 6. RT SINGLE BUFFERED MODE

DATA

BLOCKS

DATA BLOCK

BLOCK STATUS WORD

TIME TAG WORD

DATA BLOCK POINTER

RECEIVED COMMAND

WORD

DESCRIPTOR

STACKS

LOOK-UP

TABLE ADDR

LOOK-UP TABLE

(DATA BLOCK ADDR)

15

13

0

CURRENT

AREA B/A

CONFIGURATION

REGISTER

STACK

POINTERS

(See note)

Note: Lookup table is not used for mode commands when enhanced mode codes are enabled.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A42MX24-2TQ100A | 40MX and 42MX FPGA Families |

| A42MX24-2TQ100B | 40MX and 42MX FPGA Families |

| A42MX24-2VQ100 | 40MX and 42MX FPGA Families |

| A42MX24-2VQ100A | 40MX and 42MX FPGA Families |

| A42MX24-2VQ100B | 40MX and 42MX FPGA Families |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A42MX24-2TQ176 | 功能描述:IC FPGA MX SGL CHIP 36K 176-TQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:MX 產(chǎn)品培訓(xùn)模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標(biāo)準(zhǔn)包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計:6635520 輸入/輸出數(shù):270 門數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FBGA(23x23) |

| A42MX24-2TQ176I | 功能描述:IC FPGA MX SGL CHIP 36K 176-TQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:MX 產(chǎn)品培訓(xùn)模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標(biāo)準(zhǔn)包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計:6635520 輸入/輸出數(shù):270 門數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FBGA(23x23) |

| A42MX24-2TQG176 | 功能描述:IC FPGA MX SGL CHIP 36K 176-TQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:MX 產(chǎn)品培訓(xùn)模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標(biāo)準(zhǔn)包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計:6635520 輸入/輸出數(shù):270 門數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FBGA(23x23) |

| A42MX24-2TQG176I | 功能描述:IC FPGA MX SGL CHIP 36K 176-TQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:MX 產(chǎn)品培訓(xùn)模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標(biāo)準(zhǔn)包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計:6635520 輸入/輸出數(shù):270 門數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FBGA(23x23) |

| A42MX24-3PL84 | 功能描述:IC FPGA MX SGL CHIP 36K 84-PLCC RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:MX 產(chǎn)品培訓(xùn)模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標(biāo)準(zhǔn)包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計:6635520 輸入/輸出數(shù):270 門數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FBGA(23x23) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。