- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄298744 > A42MX24-2TQ100B (Electronic Theatre Controls, Inc.) 40MX and 42MX FPGA Families PDF資料下載

參數(shù)資料

| 型號(hào): | A42MX24-2TQ100B |

| 廠(chǎng)商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 40MX and 42MX FPGA Families |

| 中文描述: | 40MX和42MX FPGA系列 |

| 文件頁(yè)數(shù): | 62/93頁(yè) |

| 文件大?。?/td> | 854K |

| 代理商: | A42MX24-2TQ100B |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)當(dāng)前第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)

65

Data Device Corporation

www.ddc-web.com

BU-6474X/6484X/6486X

J-07/05-0

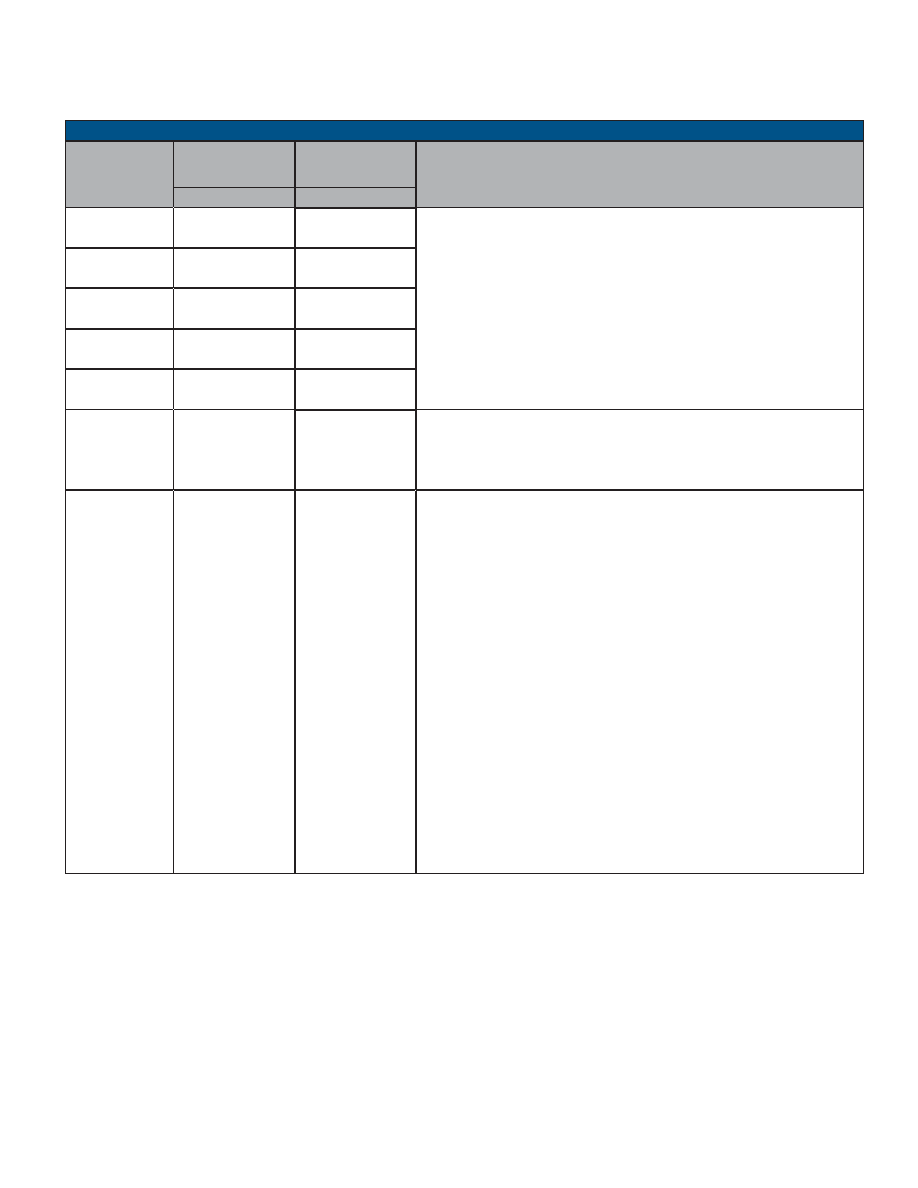

TABLE 63. RT ADDRESS

SIGNAL NAME

DESCRIPTION

BU-64840B3

BU-64860B3

BALL

BU-64743B8

BU-64843B8

BU-64863B8

BALL

RTAD4 (MSB) (I)

J16

RT Address input.

If bit 5 of Configuration Register #6, RT ADDRESS SOURCE, is programmed to

logic "0" (default), then the Mark3's RT address is provided by means of these 5

input signals. In addition, if RT ADDRESS SOURCE is logic "0", the source of RT

address parity is RTADP.

There are many methods for using these input signals for designating the Mark3's

RT address. For details, refer to the description of RT_AD_LAT.

If RT ADDRESS SOURCE is programmed to logic "1", then the Mark3's source for

its RT address and parity is under software control, via data lines D5-D0. In this

case, the RTAD4-RTAD0 and RTADP signals are not used.

J15

RTAD3 (I)

K17

M18

RTAD2 (I)

L17

J16

RTAD1 (I)

K18

L18

RTAD0 (LSB) (I)

K16

N18

RT_AD_LAT (I)

L18

RT Address Latch.

Input signal used to control the Mark3's internal RT address latch. If RT_AD_LAT is

connected to logic "0", then the Mark3 RT is configured to accept a hardwired (trans-

parent) RT address from RTAD4-RTAD0 and RTADP.

If RT_AD_LAT is initially logic "0", and then transitions to logic "1", the values pre-

sented on RTAD4-RTAD0 and RTADP will be latched internally on the rising edge

of RT_AD_LAT.

If RT_AD_LAT is connected to logic "1", then the Mark3's RT address is latchable

under host processor control. In this case, there are two possibilities: (1) If bit 5 of

Configuration Register #6, RT ADDRESS SOURCE, is programmed to logic "0"

(default), then the source of the RT Address is the RTAD4-RTAD0 and RTADP

input signals. (2) If RT ADDRESS SOURCE is programmed to logic "1", then the

source of the RT Address is the lower 6 bits of the processor data bus, D5-D1 (for

RTAD4-0) and D0 (for RTADP).

In either of these two cases (with RT_AD_LAT = "1"), the processor will cause the

RT address to be latched by: (1) Writing bit 15 of Configuration Register #3,

ENHANCED MODE ENABLE, to logic "1". (2) Writing bit 3 of Configuration

Register #4, LATCH RT ADDRESS WITH CONFIGURATION REGISTER #5, to

logic "1". (3) Writing to Configuration Register #5. In the case of RT ADDRESS

SOURCE = "1", then the values of RT address and RT address parity must be

written to the lower 6 bits of Configuration Register #5, via D5-D0. In the case

where RT ADDRESS SOURCE = "0", the bit values presented on D5-D0 become

"don't care".

P18

RTADP (I)

J18

Remote Terminal Address Parity.

This input signal must provide an odd parity sum with RTAD4-RTAD0 in order for the

RT to respond to non-broadcast commands. That is, there must be an odd number of

logic "1"s from among RTAD-4-RTAD0 and RTADP.

K18

BALL GRID ARRAY PACKAGE - SIGNAL DESCRIPTIONS BY FUNCTIONAL GROUPS (CONT.)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A42MX24-2VQ100 | 40MX and 42MX FPGA Families |

| A42MX24-2VQ100A | 40MX and 42MX FPGA Families |

| A42MX24-2VQ100B | 40MX and 42MX FPGA Families |

| A42MX24-3PQ100B | 40MX and 42MX FPGA Families |

| A42MX24-3BG100 | 40MX and 42MX FPGA Families |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A42MX24-2TQ176 | 功能描述:IC FPGA MX SGL CHIP 36K 176-TQFP RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:MX 產(chǎn)品培訓(xùn)模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標(biāo)準(zhǔn)包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計(jì):6635520 輸入/輸出數(shù):270 門(mén)數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類(lèi)型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FBGA(23x23) |

| A42MX24-2TQ176I | 功能描述:IC FPGA MX SGL CHIP 36K 176-TQFP RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:MX 產(chǎn)品培訓(xùn)模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標(biāo)準(zhǔn)包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計(jì):6635520 輸入/輸出數(shù):270 門(mén)數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類(lèi)型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FBGA(23x23) |

| A42MX24-2TQG176 | 功能描述:IC FPGA MX SGL CHIP 36K 176-TQFP RoHS:是 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:MX 產(chǎn)品培訓(xùn)模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標(biāo)準(zhǔn)包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計(jì):6635520 輸入/輸出數(shù):270 門(mén)數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類(lèi)型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FBGA(23x23) |

| A42MX24-2TQG176I | 功能描述:IC FPGA MX SGL CHIP 36K 176-TQFP RoHS:是 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:MX 產(chǎn)品培訓(xùn)模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標(biāo)準(zhǔn)包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計(jì):6635520 輸入/輸出數(shù):270 門(mén)數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類(lèi)型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FBGA(23x23) |

| A42MX24-3PL84 | 功能描述:IC FPGA MX SGL CHIP 36K 84-PLCC RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:MX 產(chǎn)品培訓(xùn)模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標(biāo)準(zhǔn)包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計(jì):6635520 輸入/輸出數(shù):270 門(mén)數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類(lèi)型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FBGA(23x23) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。