- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362097 > AD647J (Analog Devices, Inc.) Ultralow Drift, Dual BiFET Op Amp PDF資料下載

參數(shù)資料

| 型號: | AD647J |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Ultralow Drift, Dual BiFET Op Amp |

| 中文描述: | 超低漂移,雙BiFET運算放大器 |

| 文件頁數(shù): | 2/8頁 |

| 文件大?。?/td> | 150K |

| 代理商: | AD647J |

–2–

REV. 0

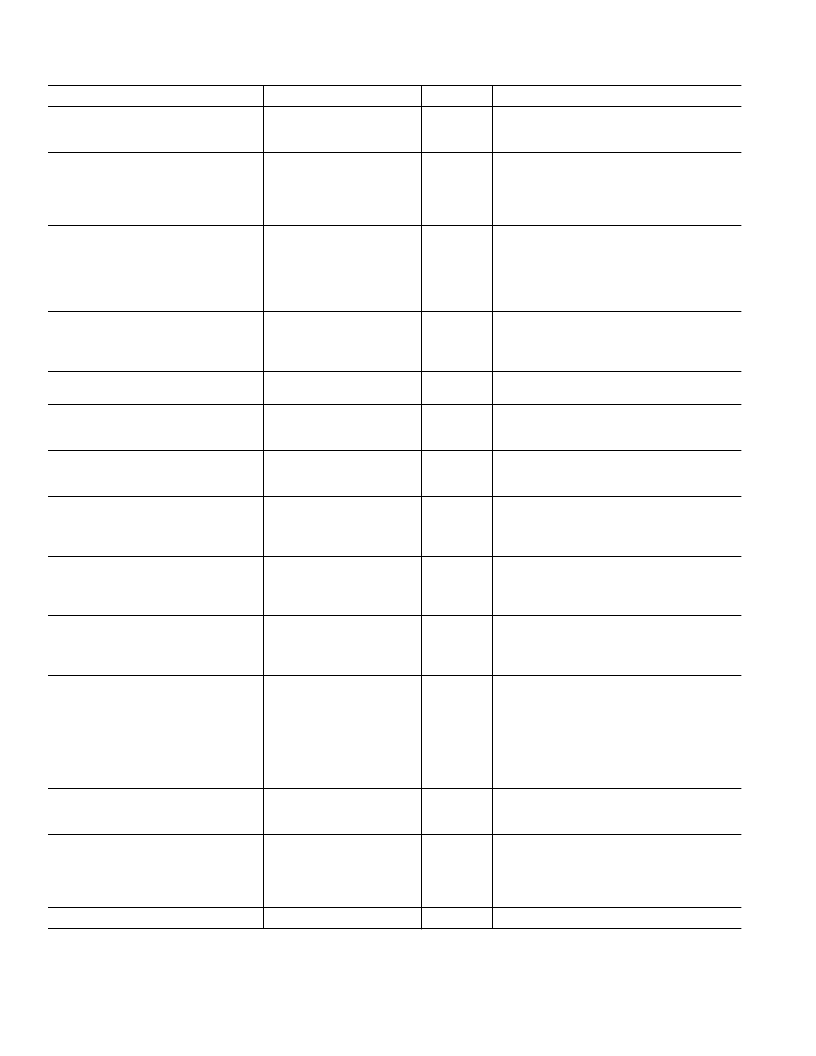

AD6472–SPECIFICATIONS

(T

A

= T

MN

to T

MAX

unless otherwse noted)

P

arameter

Min

T yp

Max

Units

Condition

T RANSMIT CHANNEL

SNR

T HD

68

66

71

71

dB

dB

T he complete transmit path spectrum and pulse

shape comply with ET SI requirements.

T RANSMIT DAC

Clock Frequency

Resolution

Update Rate

Output Voltage

T he transmit DAC maximum update rate is half

the maximum output data rate, i.e., 1168 kHz.

T he maximum transmit clock is 16

×

1168 =

18.688 MHz.

18.688

MHz

Bits

kHz

V p-p Diff

12

1168

2

T RANSMIT FILT ER

Corner Frequency (3 dB)

1

320

535

±

5

9.53

3.53

kHz

kHz

%

dB

dB

MODE_SEL1 = 0

MODE_SEL1 = 1

Accuracy

Gain

±

10

LINE DRIVER

VCM

Output Power

Output Voltage

2.5

13.5

6

V

dBm

V p-p Diff

T ransformer T urns Ratio = 1:2.3 at 50 kHz

When Loaded by ET SI (RT R/T M3036)

HDSL T est Loops

T RANSMIT VOLT AGE LEVEL

6

3

V p-p Diff

V p-p Diff

T X _GAIN = 0

T X _GAIN = 1

RECEIVE CHANNEL

SNR

T HD

68

66

71

71

dB

dB

HYBRID INT ERFACE

Input Voltage Range

Input Impedance

V

CM

= 2.5 V. See Figure 3

5

V p-p Diff

k

10

PROGRAMMABLE GAIN AMPLIFIER

Overall Gain Accuracy

Gain Step

Gain Step Accuracy

Condition –6 dB to +9 dB

±

1

3

±

0.25

dB

dB

dB

RECEIVE FILT ER

Corner Frequency (–3 dB)

1

320

640

±

5

kHz

kHz

%

MODE_SEL1 = 0

MODE_SEL1 = 1

Accuracy

±

10

T IMING RECOVERY DAC

Resolution

Output Low

Output High

7

Bits

V

V

Guaranteed Monotonic

0.5

4.5

DIGIT AL INT ERFACE

Input Logic High, V

IH

Input Logic L

OW

, V

IL

Output Logic High, V

OH

Output Logic Low, V

OL

Input Logic High, V

IH

Input Logic Low, V

IL

Output Logic High, V

OH

POWER SUPPLY VOLT AGE

5 V Supply, V

MIN

to V

MAX

3.3

V

V

V

V

V

V

V

0.8

V

DD

– 0.3

0.4

3.3 V Supply, V

MIN

to V

MAX

2.0

0.2

V

DD

– 0.3

V

MIN

to V

MAX

5 V Supply

3.3 V Supply

4.75

3.15

5

3.3

5.25

3.45

V

V

POWER SUPPLY CURRENT

Normal Mode, Excl. Driver

OVRSAMP Mode

Line Driver

Low Power Mode

V

to V

, T

to T

5 V Supply, MODE_SEL1 = 0

5 V Supply, MODE_SEL1 = 1, MODE_SEL0 = 1

With 50

Differential Load

65

73

50

17

mA

mA

mA

mA

OPERAT ING T EMPERAT URE RANGE

–40

+85

°

C

T

MIN

to T

MAX

NOT ES

1

T he ADC clock period t(1

÷

f) is used for the dynamic tuning of the T x and Rx filters.

Specifications subject to change without notice.

Powered by ICminer.com Electronic-Library Service CopyRight 2003

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD647K | Ultralow Drift, Dual BiFET Op Amp |

| AD647L | Ultralow Drift, Dual BiFET Op Amp |

| AD647S | Ultralow Drift, Dual BiFET Op Amp |

| AD647SE | Ultralow Drift, Dual BiFET Op Amp |

| AD647SH | Ultralow Drift, Dual BiFET Op Amp |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD647JH | 制造商:Rochester Electronics LLC 功能描述:PRECISION DUAL OP AMP IC - Bulk 制造商:ANALOG 功能描述:AD647JH 制造商:Analog Devices 功能描述: |

| AD647K | 制造商:AD 制造商全稱:Analog Devices 功能描述:Ultralow Drift, Dual BiFET Op Amp |

| AD647KH | 制造商:Rochester Electronics LLC 功能描述:PRECISION DUAL OP AMP IC - Bulk |

| AD647L | 制造商:AD 制造商全稱:Analog Devices 功能描述:Ultralow Drift, Dual BiFET Op Amp |

| AD647LH | 制造商:AD 制造商全稱:Analog Devices 功能描述:Ultralow Drift, Dual BiFET Op Amp |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。