- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362097 > AD647KH (ANALOG DEVICES INC) Ultralow Drift, Dual BiFET Op Amp PDF資料下載

參數(shù)資料

| 型號: | AD647KH |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 運動控制電子 |

| 英文描述: | Ultralow Drift, Dual BiFET Op Amp |

| 中文描述: | DUAL OP-AMP, 1000 uV OFFSET-MAX, 1 MHz BAND WIDTH, MBCY8 |

| 封裝: | HERMETIC SEALED, METAL CAN, TO-99, 8 PIN |

| 文件頁數(shù): | 6/8頁 |

| 文件大小: | 150K |

| 代理商: | AD647KH |

AD6472

–6–

REV. 0

T able III.

Receive Channel

MODE _SE L1

Filter Control Bit

MODE _SE L0

Receive Clock

Frequency (kHz)

3 dB Frequency

(kHz)

0

0

1

1

0

1

0

1

1168/2

Reserved

1160

1160

×

2

Rx = 320/T x = 320

Reserved

Rx = 640/T x = 535

Rx = 640/T x = 535

T able IV. Configuration Control

Pin

Mnemonic

Logic 0 = Function

Logic 1 = Function

5

6

7

8

AA_FLT R_BP

PWRDN

ADC_BUF_BP

T X _GAIN_SEL

Receive Filter in Circuit

Low Power Selected

ADC Buffer in Circuit

0 dB Attenuation

Receive Filter Bypassed

Normal Operating Mode

ADC Buffer Bypassed

6 dB Attenuation

9

11

13

T X _DRVR_BP

T X _LPF_BP

LOOPBACK

Line Driver in Circuit

T ransmit Filter in Circuit

Normal Operation

Line Driver Bypassed

T ransmit Circuit Bypassed

Analog Loopback Selected

Receive Channel

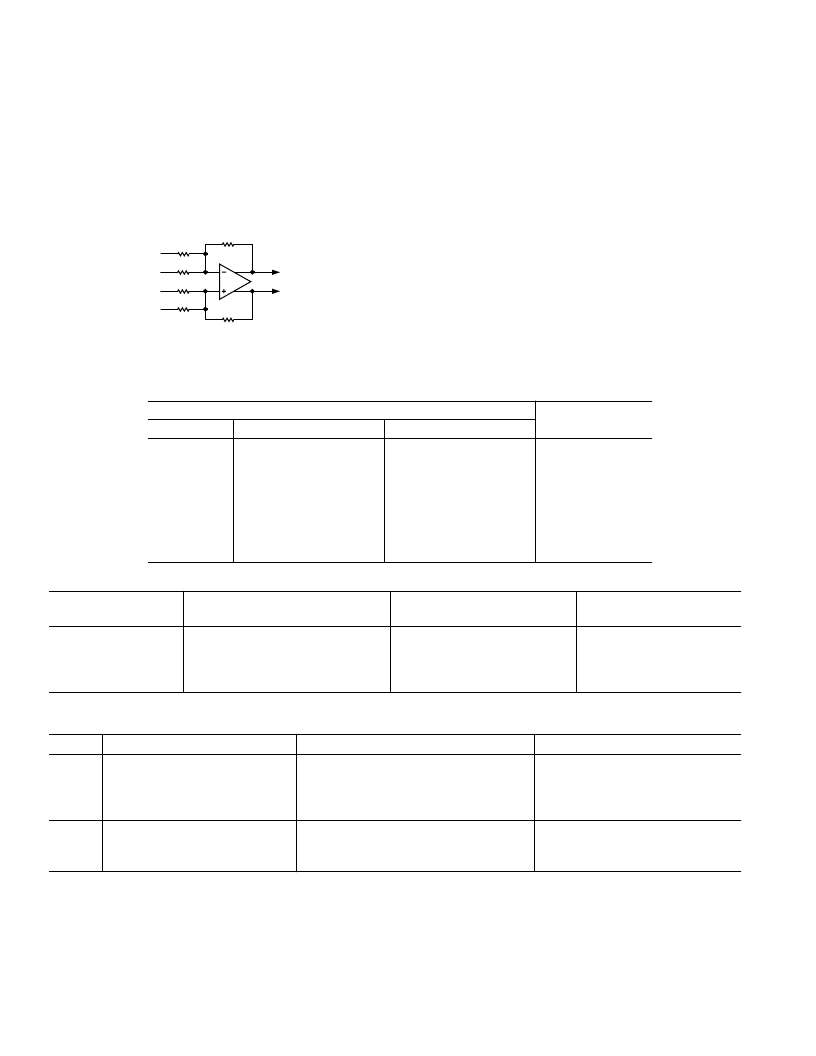

Hybrid Amplifier

T he hybrid amplifier performs balanced to unbalanced

conversion.

Programmable Gain Amplifier (PGA)

T he PGA can be programmed to amplify the receive signal

from between –6 dB and 9 dB. Refer to T able II for PGA gain

control information.

10k

V

10k

V

10k

V

10k

V

10k

V

10k

V

TO PGA

HYB_IN1_A

HYB_IN1_B

HYB_IN2_A

HYB_IN2_B

Figure 3.

T ransmit and Receive Filters

Refer to T able III for transmit and receive channels filter

control information. T he receive channel filters meet ET SI

requirements.

Analog-to-Digital Converter (ADC)

T he receive channel ADC has a pipeline architecture with 12-

bit resolution. T he ADC can be clocked at 2320 kHz, maxi-

mum. Output data is provided in 2s complement form.

T iming Recovery D/A

T he AD6472 has an integrated D/A converter to control an

external VCX O used for timing recovery. T he D/A is 7 bits and

monotonic. T he D/A accepts 7 bits inverted format input data

serially with the MSB first.

Configuration Control

T able IV presents control information that you use to configure

the AD6472.

T able II.

Gain Control Bit

PGA_GC2

Binary Count

GAIN (dB)

PGA_GC1

PGA_GC0

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

–6

–3

0

3

6

9

9

9

Powered by ICminer.com Electronic-Library Service CopyRight 2003

相關PDF資料 |

PDF描述 |

|---|---|

| AD647LH | MLT Series Linear Position Transducer, 152,4 mm [6.0 in] Electrical Travel, Less than 0.5 % Linearity, Item Number F38000206 |

| AD647 | Ultralow Drift, Dual BiFET Op Amp |

| AD647J | Ultralow Drift, Dual BiFET Op Amp |

| AD647K | Ultralow Drift, Dual BiFET Op Amp |

| AD647L | Ultralow Drift, Dual BiFET Op Amp |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD647L | 制造商:AD 制造商全稱:Analog Devices 功能描述:Ultralow Drift, Dual BiFET Op Amp |

| AD647LH | 制造商:AD 制造商全稱:Analog Devices 功能描述:Ultralow Drift, Dual BiFET Op Amp |

| AD647S | 制造商:AD 制造商全稱:Analog Devices 功能描述:Ultralow Drift, Dual BiFET Op Amp |

| AD647SE | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD647SE/883B | 制造商:Rochester Electronics LLC 功能描述:PRECISION DUAL OP AMP IC - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。