- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄8575 > AD669BRZ-REEL (Analog Devices Inc)IC DAC 16BIT MONO VREF 28-SOIC PDF資料下載

參數(shù)資料

| 型號: | AD669BRZ-REEL |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 11/12頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC DAC 16BIT MONO VREF 28-SOIC |

| 產(chǎn)品變化通告: | AD669 Improvement Change 11/Jul/2012 |

| 標準包裝: | 1 |

| 系列: | DACPORT® |

| 設置時間: | 10µs |

| 位數(shù): | 16 |

| 數(shù)據(jù)接口: | 并聯(lián) |

| 轉(zhuǎn)換器數(shù)目: | 1 |

| 電壓電源: | 雙 ± |

| 功率耗散(最大): | 625mW |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 28-SOIC(0.295",7.50mm 寬) |

| 供應商設備封裝: | 28-SOIC W |

| 包裝: | 標準包裝 |

| 輸出數(shù)目和類型: | * |

| 采樣率(每秒): | 167k |

| 其它名稱: | AD669BRZ-REELDKR |

AD669

REV. A

–8–

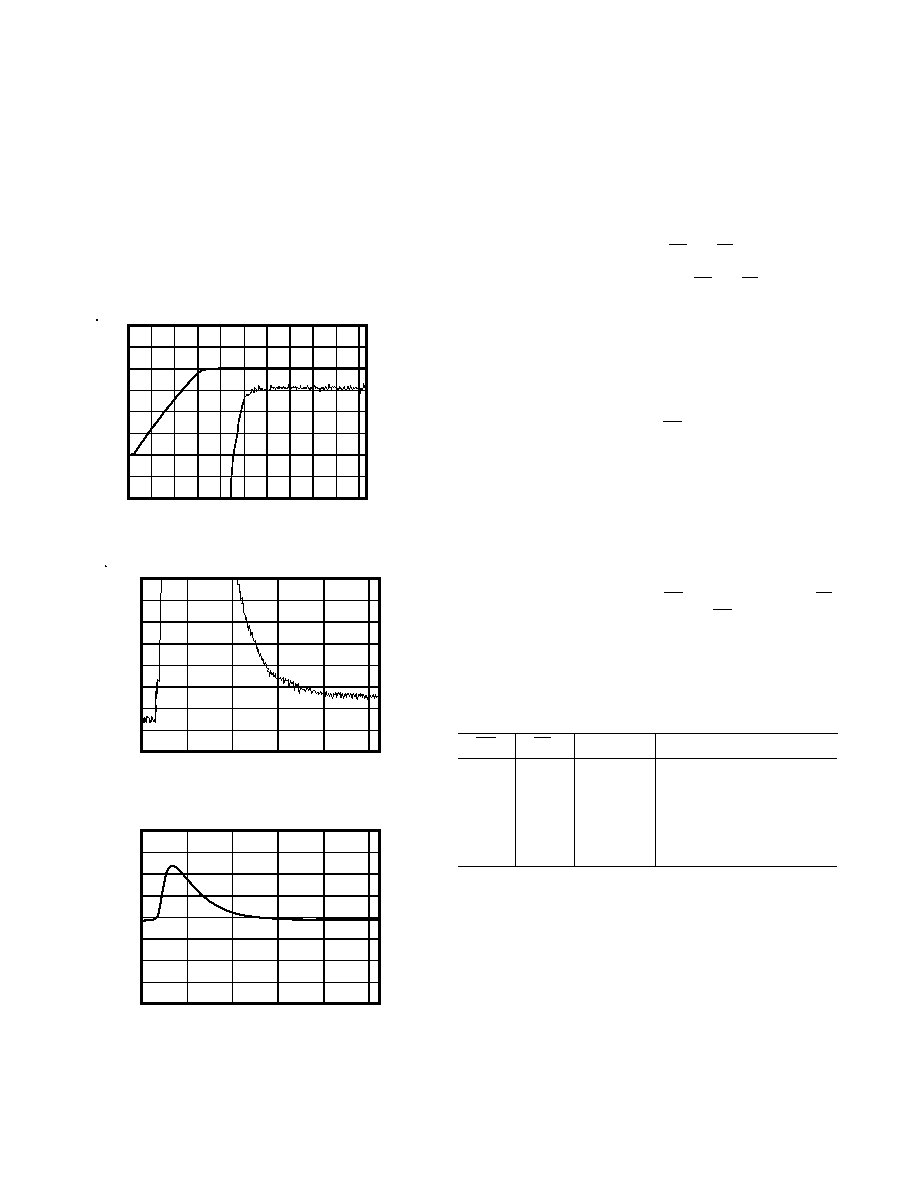

OUTPUT SETTLING AND GLITCH

The AD669’s output buffer amplifier typically settles to within

0.0008% FS (l/2 LSB) of its final value in 8

s for a full-scale

step. Figures 7a and 7b show settling for a full-scale and an LSB

step, respectively, with a 2 k

, 1000 pF load applied. The guar-

anteed maximum settling time at +25

°C for a full-scale step is

13

s with this load. The typical settling time for a 1 LSB step is

2.5

s.

The digital-to-analog glitch impulse is specified as 15 nV-s typi-

cal. Figure 7c shows the typical glitch impulse characteristic at

the code 011 . . . 111 to 100 . . . 000 transition when loading

the second rank register from the first rank register.

20

–10

0

+10

10

600

400

200

0

–200

–400

–600

VOLTS

s

V

a. –10 V to +10 V Full-Scale Step Settling

5

0

600

400

200

–200

–400

–600

s

V

1

23

4

b. LSB Step Settling

5

0

+10

–10

s

mV

1

23

4

c. D-to-A Glitch Impulse

Figure 7. Output Characteristics

DIGITAL CIRCUIT DETAILS

The bus interface logic of the AD669 consists of two indepen-

dently addressable registers in two ranks. The first rank consists

of a 16-bit register which is loaded directly from a 16-bit micro-

processor bus. Once the 16-bit data word has been loaded in the

first rank, it can be loaded into the 16-bit register of the second

rank. This double-buffered organization avoids the generation of

spurious analog output values.

The first rank latch is controlled by CS and L1. Both of these

inputs are active low and are level-triggered. This means that

data present during the time when both CS and L1 are low will

enter the latch. When either one of these signals returns high,

the data is latched.

The second rank latch is controlled by LDAC. This input is ac-

tive high and is also level-triggered. Data that is present when

LDAC is high will enter the latch, and hence the DAC will

change state. When this pin returns low, the data is latched in

the DAC.

Note that LDAC is not gated with CS or any other control sig-

nal. This makes it possible to simultaneously update all of the

AD669’s present in a multi-DAC system by tying the LDAC

pins together. After the first rank register of each DAC has been

individually loaded and latched, the second rank registers are

then brought high together, updating all of the DACs at the

same time. To reduce bit skew, it is suggested to leave 100 ns

between the first rank load and the second rank load.

The first rank latch and second rank latch can be used together

in a master-slave or edge-triggered configuration. This mode of

operation occurs when LDAC and CS are tied together with L1

tied to ground. Rising edges on the LDAC-CS pair will update

the DAC with the data presented preceding the edge. The tim-

ing diagram for operation in this mode can be seen in Figure lb.

Note, however, that the sum of tLOW and tHIGH must be long

enough to allow the DAC output to settle to its new value.

Table I. AD669 Truth Table

CS

L1

LDAC

Operation

0

X

First Rank Enable

X

1

X

First Rank Latched

1

X

First Rank Latched

X

1

Second Rank Enabled

X

0

Second Rank Latched

0

1

All Latches Transparent

“X” = Don’t Care

It is possible to make the second rank register transparent by ty-

ing Pin 23 high. Any data appearing in the first rank register will

then appear at the output of the DAC. It should be noted, how-

ever, that the deskewing provided by the second rank latch is

then defeated, and glitch impulse may increase. If it is desired to

make both registers transparent, this can be done by tying Pins

5 and 6 low and Pin 23 high. Table I shows the truth table for

the AD669, while the timing diagram is found in Figure 1.

INPUT CODING

The AD669 uses positive-true binary input coding. Logic “1” is

represented by an input voltage greater than 2.0 V, and Logic

“0” is defined as an input voltage less than 0.8 V.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VE-B5M-MU | CONVERTER MOD DC/DC 10V 200W |

| NE592D8R2G | IC AMP VIDEO 2STAGE DIFF 8-SOIC |

| MAX4393EUB+T | IC OP AMP 85MHZ R-R 10-UMAX |

| MAX9505ETE+T | IC VIDEO AMP W/FILTER 16-TQFN |

| LTC1597-1ACG | IC D/A CONV 16BIT PAR 28-SSOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD669SQ | 功能描述:數(shù)模轉(zhuǎn)換器- DAC IC MONO 16-BIT RoHS:否 制造商:Analog Devices 轉(zhuǎn)換器數(shù)量:4 DAC 輸出端數(shù)量:4 轉(zhuǎn)換速率: 分辨率:12 bit 接口類型:Serial (I2C) 穩(wěn)定時間: 最大工作溫度:+ 105 C 安裝風格: 封裝 / 箱體:TSSOP 封裝:Reel |

| AD669SQ/883B | 功能描述:數(shù)模轉(zhuǎn)換器- DAC IC MONO 16-BIT RoHS:否 制造商:Analog Devices 轉(zhuǎn)換器數(shù)量:4 DAC 輸出端數(shù)量:4 轉(zhuǎn)換速率: 分辨率:12 bit 接口類型:Serial (I2C) 穩(wěn)定時間: 最大工作溫度:+ 105 C 安裝風格: 封裝 / 箱體:TSSOP 封裝:Reel |

| AD66BS | 制造商:POP 功能描述: 制造商:RIVETS 功能描述: |

| AD67 | 制造商:MQP (ELECTRONICS) 功能描述:ADAPTOR DIL 28WAY 制造商:MQP (ELECTRONICS) 功能描述:ADAPTOR, DIL, 28WAY 制造商:MQP (ELECTRONICS) 功能描述:ADAPTOR, DIL, 28WAY; Connector Type:Adaptor; No. of Contacts:28; Row Pitch:0.6"; Contact Termination:Through Hole Vertical; SVHC:No SVHC (19-Dec-2012); Connector Mounting Orientation:PC Board; No. of Ways:28; Package / Case:DIL; Pin ;RoHS Compliant: Yes |

| AD67 | 制造商:MQP (ELECTRONICS) 功能描述:ADAPTOR DIL 28 WAY |

發(fā)布緊急采購,3分鐘左右您將得到回復。