- 您現在的位置:買賣IC網 > PDF目錄384089 > ADC1210S080HN (NXP Semiconductors N.V.) Single 12-bit ADC 80 Msps CMOS or LVDS DDR digital outputs PDF資料下載

參數資料

| 型號: | ADC1210S080HN |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類: | 外設及接口 |

| 英文描述: | Single 12-bit ADC 80 Msps CMOS or LVDS DDR digital outputs |

| 封裝: | ADC1210S080HN/C1<SOT618-1 (HVQFN40)|<<http://www.nxp.com/packages/SOT618-1.html<1<Always Pb-free,;ADC1210S080HN/C1<SOT618-1 (HVQFN40)|<<http://www.nxp.com/packages/SOT618 |

| 文件頁數: | 9/39頁 |

| 文件大小: | 283K |

| 代理商: | ADC1210S080HN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxx x x x xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xx xx xxxxx

xxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxx x x

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxx

xxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxx xxx

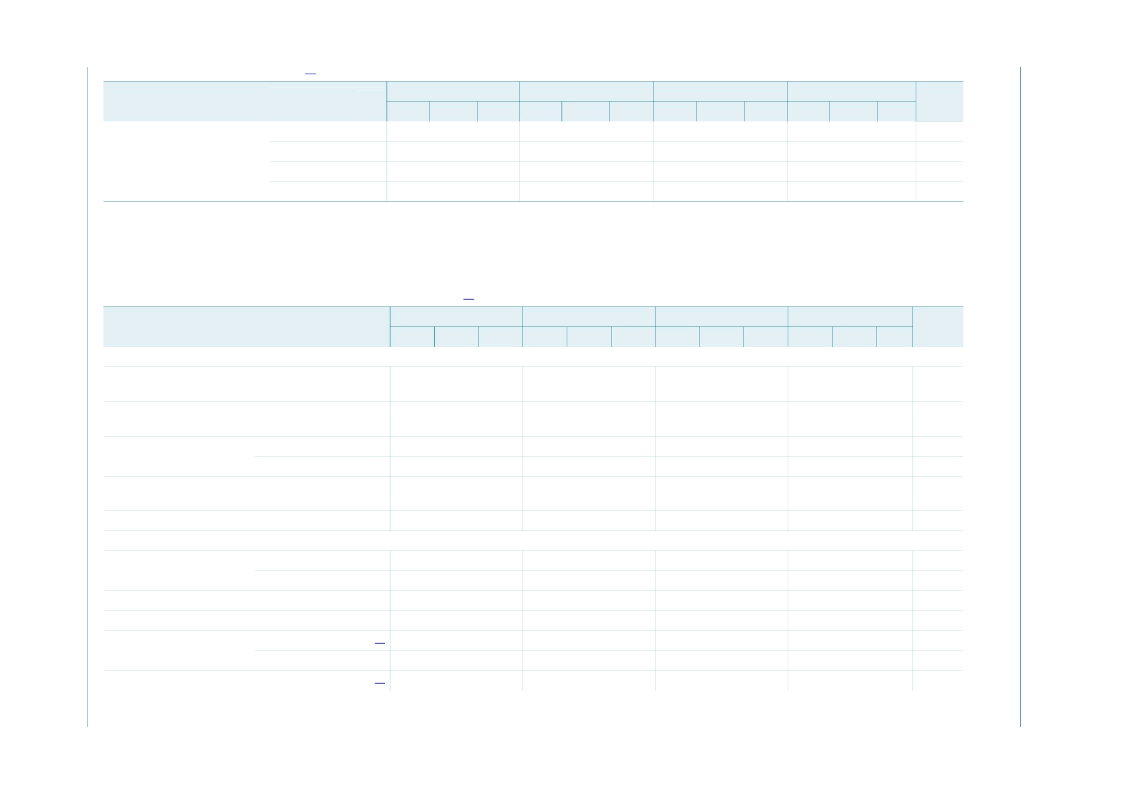

Dynamic characteristics

[1]

…continued

Parameter

Conditions

ADC1210S065

ADC1210S080

Min

Typ

Max

Min

A

A

P

R

9

N

A

S

[1]

Typical values measured at V

DDA

= 3 V, V

DDO

= 1.8 V, T

amb

= 25

C and C

L

= 5 pF; minimum and maximum values are across the full temperature range T

amb

=

40

C to +85

C

at V

DDA

= 3 V, V

DDO

= 1.8 V; V

INP

V

INM

=

1 dBFS; internal reference mode; applied to CMOS and LVDS interface; unless otherwise specified.

10.2 Clock and digital output timing

IMD

Intermodulation

distortion

f

i

= 3 MHz

f

i

= 30 MHz

f

i

= 70 MHz

f

i

= 170 MHz

-

-

-

-

89

88

87

84

-

-

-

-

-

-

-

-

89

88

87

85

-

-

-

-

-

-

-

-

88

88

86

83

-

-

-

-

-

-

-

-

89

88

86

84

-

-

-

-

dBc

dBc

dBc

dBc

Table 7.

Symbol

ADC1210S105

Min

Typ

ADC1210S125

Min

Typ

Unit

Typ

Max

Max

Max

Table 8.

Symbol

Clock input and digital output timing characteristics

[1]

Parameter

Conditions

ADC1210S065

Min

Typ

ADC1210S080

Min

Typ

ADC1210S105

Min

Typ

ADC1210S125

Min

Typ

Unit

Max

Max

Max

Max

Clock timing input: pins CLKP and CLKM

f

clk

clock

frequency

t

lat(data)

data latency

time

clk

clock duty

cycle

40

-

65

60

-

80

75

-

105

100

-

125

MHz

-

13.5

-

-

13.5

-

-

13.5

-

-

13.5

-

clock

cycles

%

%

ns

DCS_EN = logic 1

DCS_EN = logic 0

30

45

-

50

50

0.8

70

55

-

30

45

-

50

50

0.8

70

55

-

30

45

-

50

50

0.8

70

55

-

30

45

-

50

50

0.8

70

55

-

t

d(s)

sampling

delay time

wake-up time

t

wake

CMOS mode timing output: pins D11 to D0 and DAV

t

PD

propagation

delay

-

76

-

-

76

-

-

76

-

-

76

-

s

DATA

DAV

13.6

-

-

-

0.39

0.26

0.19

14.9

4.2

12.5

3.4

-

-

-

16.4

-

-

-

2.4

2.4

2.4

11.9

-

-

-

0.39

0.26

0.19

12.9

3.6

9.8

3.3

-

-

-

14.4

-

-

-

2.4

2.4

2.4

8.0

-

-

-

0.39

0.26

0.19

10.8

3.3

6.8

3.1

-

-

-

12.4

-

-

-

2.4

2.4

2.4

8.2

-

-

-

0.39

0.26

0.19

9.7

3.4

5.6

2.8

-

-

-

11.3

-

-

-

2.4

2.4

2.4

ns

ns

ns

ns

ns

ns

ns

t

su

t

h

t

r

set-up time

hold time

rise time

DATA

DAV

DATA

[2]

t

f

fall time

[2]

相關PDF資料 |

PDF描述 |

|---|---|

| ADC1210S105HN | Single 12-bit ADC 105 Msps CMOS or LVDS DDR digital outputs |

| ADC1210S125HN | Single 12-bit ADC 125 Msps CMOS or LVDS DDR digital outputs |

| ADC1215S065HN | Single 12-bit ADC 65 Msps with Input Buffer CMOS or LVDS DDR digital outputs |

| ADC1215S065HN | Single 12-bit ADC 65 Msps with Input Buffer CMOS or LVDS DDR digital outputs |

| ADC1215S080HN | Single 12-bit ADC 80 Msps with Input Buffer CMOS or LVDS DDR digital outputs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADC1210S080HN,551 | 功能描述:模數轉換器 - ADC 12bit 70dB 125MSPS RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| ADC1210S080HN/C1 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Single 12-bit ADC; 65 Msps, 80 Msps, 105 Msps or 125 Msps; CMOS or LVDS DDR digital outputs |

| ADC1210S080HN/C1,5 | 功能描述:模數轉換器 - ADC 12bit 70dB 125MSPS RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| ADC1210S080HN-C1 | 制造商:Integrated Device Technology Inc 功能描述:HVQFN40 - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。