- 鎮ㄧ従(xi脿n)鍦ㄧ殑浣嶇疆锛�璨疯常IC缍�(w菐ng) > PDF鐩寗4533 > AGLP030V2-VQ128 (Microsemi SoC)IC FPGA IGLOO PLUS 30K 128-VQFN PDF璩囨枡涓嬭級

鍙冩暩(sh霉)璩囨枡

| 鍨嬭櫉锛� | AGLP030V2-VQ128 |

| 寤犲晢锛� | Microsemi SoC |

| 鏂囦欢闋佹暩(sh霉)锛� | 89/134闋� |

| 鏂囦欢澶�?銆�?/td> | 0K |

| 鎻忚堪锛� | IC FPGA IGLOO PLUS 30K 128-VQFN |

| 妯�(bi膩o)婧�(zh菙n)鍖呰锛� | 90 |

| 绯诲垪锛� | IGLOO PLUS |

| 閭忚集鍏冧欢/鍠厓鏁�(sh霉)锛� | 792 |

| 杓稿叆/杓稿嚭鏁�(sh霉)锛� | 101 |

| 闁€鏁�(sh霉)锛� | 30000 |

| 闆绘簮闆诲锛� | 1.14 V ~ 1.575 V |

| 瀹夎椤炲瀷锛� | 琛ㄩ潰璨艰 |

| 宸ヤ綔婧害锛� | 0°C ~ 70°C |

| 灏佽/澶栨锛� | 128-TQFP |

| 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁濓細 | 128-VTQFP锛�14x14锛� |

绗�1闋�绗�2闋�绗�3闋�绗�4闋�绗�5闋�绗�6闋�绗�7闋�绗�8闋�绗�9闋�绗�10闋�绗�11闋�绗�12闋�绗�13闋�绗�14闋�绗�15闋�绗�16闋�绗�17闋�绗�18闋�绗�19闋�绗�20闋�绗�21闋�绗�22闋�绗�23闋�绗�24闋�绗�25闋�绗�26闋�绗�27闋�绗�28闋�绗�29闋�绗�30闋�绗�31闋�绗�32闋�绗�33闋�绗�34闋�绗�35闋�绗�36闋�绗�37闋�绗�38闋�绗�39闋�绗�40闋�绗�41闋�绗�42闋�绗�43闋�绗�44闋�绗�45闋�绗�46闋�绗�47闋�绗�48闋�绗�49闋�绗�50闋�绗�51闋�绗�52闋�绗�53闋�绗�54闋�绗�55闋�绗�56闋�绗�57闋�绗�58闋�绗�59闋�绗�60闋�绗�61闋�绗�62闋�绗�63闋�绗�64闋�绗�65闋�绗�66闋�绗�67闋�绗�68闋�绗�69闋�绗�70闋�绗�71闋�绗�72闋�绗�73闋�绗�74闋�绗�75闋�绗�76闋�绗�77闋�绗�78闋�绗�79闋�绗�80闋�绗�81闋�绗�82闋�绗�83闋�绗�84闋�绗�85闋�绗�86闋�绗�87闋�绗�88闋�鐣�(d膩ng)鍓嶇89闋�绗�90闋�绗�91闋�绗�92闋�绗�93闋�绗�94闋�绗�95闋�绗�96闋�绗�97闋�绗�98闋�绗�99闋�绗�100闋�绗�101闋�绗�102闋�绗�103闋�绗�104闋�绗�105闋�绗�106闋�绗�107闋�绗�108闋�绗�109闋�绗�110闋�绗�111闋�绗�112闋�绗�113闋�绗�114闋�绗�115闋�绗�116闋�绗�117闋�绗�118闋�绗�119闋�绗�120闋�绗�121闋�绗�122闋�绗�123闋�绗�124闋�绗�125闋�绗�126闋�绗�127闋�绗�128闋�绗�129闋�绗�130闋�绗�131闋�绗�132闋�绗�133闋�绗�134闋�

IGLOO PLUS DC and Switching Characteristics

2-44

Revision 16

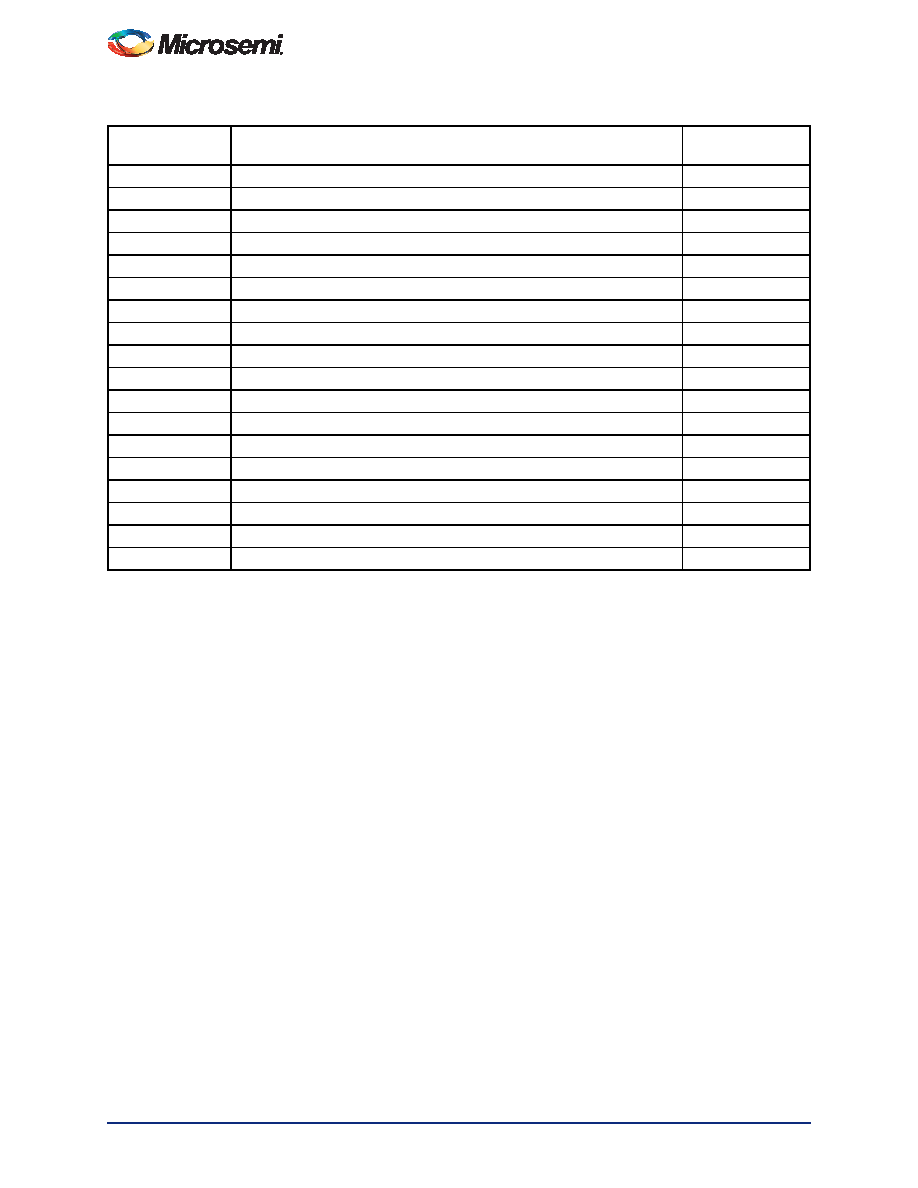

Table 2-73 Parameter Definition and Measuring Nodes

Parameter Name

Parameter Definition

Measuring Nodes

(from, to)*

tOCLKQ

Clock-to-Q of the Output Data Register

HH, DOUT

tOSUD

Data Setup Time for the Output Data Register

FF, HH

tOHD

Data Hold Time for the Output Data Register

FF, HH

tOCLR2Q

Asynchronous Clear-to-Q of the Output Data Register

LL, DOUT

tOREMCLR

Asynchronous Clear Removal Time for the Output Data Register

LL, HH

tORECCLR

Asynchronous Clear Recovery Time for the Output Data Register

LL, HH

tOECLKQ

Clock-to-Q of the Output Enable Register

HH, EOUT

tOESUD

Data Setup Time for the Output Enable Register

JJ, HH

tOEHD

Data Hold Time for the Output Enable Register

JJ, HH

tOECLR2Q

Asynchronous Clear-to-Q of the Output Enable Register

II, EOUT

tOEREMCLR

Asynchronous Clear Removal Time for the Output Enable Register

II, HH

tOERECCLR

Asynchronous Clear Recovery Time for the Output Enable Register

II, HH

tICLKQ

Clock-to-Q of the Input Data Register

AA, EE

tISUD

Data Setup Time for the Input Data Register

CC, AA

tIHD

Data Hold Time for the Input Data Register

CC, AA

tICLR2Q

Asynchronous Clear-to-Q of the Input Data Register

DD, EE

tIREMCLR

Asynchronous Clear Removal Time for the Input Data Register

DD, AA

tIRECCLR

Asynchronous Clear Recovery Time for the Input Data Register

DD, AA

Note: *See Figure 2-13 on page 2-43 for more information.

鐩搁棞(gu膩n)PDF璩囨枡 |

PDF鎻忚堪 |

|---|---|

| BR93L46RFV-WE2 | IC EEPROM 1KBIT 2MHZ 8SSOP |

| AGLP030V2-VQG128 | IC FPGA IGLOO PLUS 30K 128-VQFN |

| RBB75DHBR | CONN EDGECARD 150PS R/A .050 DIP |

| A3PN250-Z2VQG100 | IC FPGA NANO 250K GATES 100-VQFP |

| A3PN250-Z2VQ100 | IC FPGA NANO 250K GATES 100-VQFP |

鐩搁棞(gu膩n)浠g悊鍟�/鎶€琛�(sh霉)鍙冩暩(sh霉) |

鍙冩暩(sh霉)鎻忚堪 |

|---|---|

| AGLP030V2-VQ128I | 鍔熻兘鎻忚堪:IC FPGA IGLOO PLUS 30K 128-VQFN RoHS:鍚� 椤炲垾:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - FPGA锛堢従(xi脿n)鍫村彲绶ㄧ▼闁€闄e垪锛� 绯诲垪:IGLOO PLUS 妯�(bi膩o)婧�(zh菙n)鍖呰:152 绯诲垪:IGLOO PLUS LAB/CLB鏁�(sh霉):- 閭忚集鍏冧欢/鍠厓鏁�(sh霉):792 RAM 浣嶇附瑷�:- 杓稿叆/杓稿嚭鏁�(sh霉):120 闁€鏁�(sh霉):30000 闆绘簮闆诲:1.14 V ~ 1.575 V 瀹夎椤炲瀷:琛ㄩ潰璨艰 宸ヤ綔婧害:-40°C ~ 85°C 灏佽/澶栨:289-TFBGA锛孋SBGA 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁�:289-CSP锛�14x14锛� |

| AGLP030-V2VQ289 | 鍒堕€犲晢:ACTEL 鍒堕€犲晢鍏ㄧū:Actel Corporation 鍔熻兘鎻忚堪:IGLOO PLUS Low-Power Flash FPGAs with FlashFreeze Technology |

| AGLP030-V2VQ289ES | 鍒堕€犲晢:ACTEL 鍒堕€犲晢鍏ㄧū:Actel Corporation 鍔熻兘鎻忚堪:IGLOO PLUS Low-Power Flash FPGAs with FlashFreeze Technology |

| AGLP030-V2VQ289I | 鍒堕€犲晢:ACTEL 鍒堕€犲晢鍏ㄧū:Actel Corporation 鍔熻兘鎻忚堪:IGLOO PLUS Low-Power Flash FPGAs with FlashFreeze Technology |

| AGLP030-V2VQ289PP | 鍒堕€犲晢:ACTEL 鍒堕€犲晢鍏ㄧū:Actel Corporation 鍔熻兘鎻忚堪:IGLOO PLUS Low-Power Flash FPGAs with FlashFreeze Technology |

鐧�(f膩)甯冪穵鎬ラ噰璩�锛�3鍒嗛悩宸﹀彸鎮ㄥ皣寰楀埌鍥炲京(f霉)銆�