- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄42888 > AGR21180EU (LSI CORP) S BAND, Si, N-CHANNEL, RF POWER, MOSFET PDF資料下載

參數(shù)資料

| 型號(hào): | AGR21180EU |

| 廠商: | LSI CORP |

| 元件分類: | 功率晶體管 |

| 英文描述: | S BAND, Si, N-CHANNEL, RF POWER, MOSFET |

| 封裝: | SURFACE MOUNT PACKAGE-4 |

| 文件頁(yè)數(shù): | 1/11頁(yè) |

| 文件大?。?/td> | 603K |

| 代理商: | AGR21180EU |

Preliminary Data Sheet

November 2003

AGR21180E

180 W, 2.110 GHz—2.170 GHz, N-Channel E-Mode, Lateral MOSFET

Introduction

The AGR21180E is a high-voltage, gold-metalized,

laterally diffused metal oxide semiconductor

(LDMOS) RF power transistor suitable for wideband

code division multiple access (W-CDMA), single and

multicarrier class AB wireless base station power

amplifier applications.

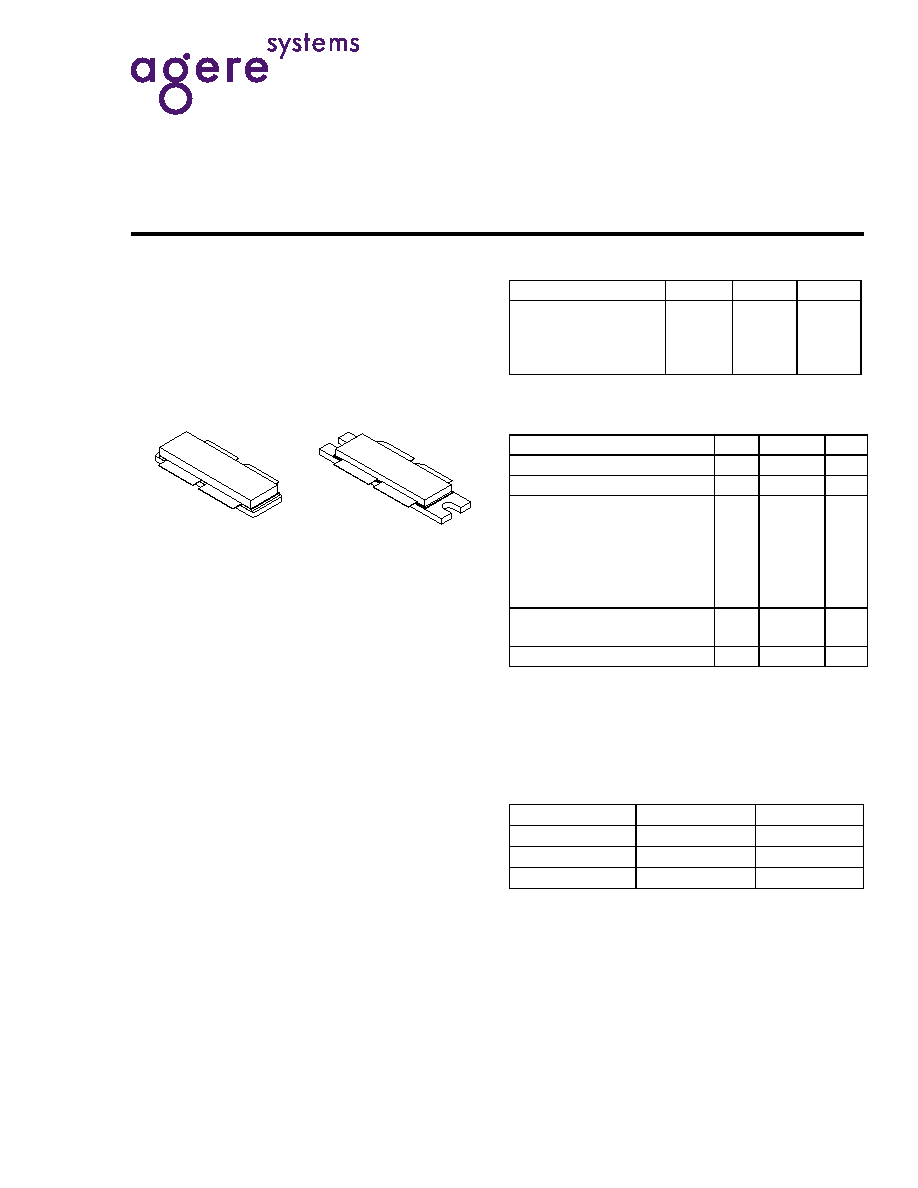

Figure 1. Available Packages

Features

I Typical performance for two carrier 3GPP

W-CDMA systems. F1 = 2135 MHz and

F2 = 2145 MHz with 3.84 MHz channel bandwidth

(BW), adjacent channel BW = 3.84 MHz at

F1 – 5 MHz and F2 + 5 MHz. Third-order distortion

is measured over 3.84 MHz BW at F1 – 10 MHz

and F2 + 10 MHz. Typical peak-to-average (P/A)

ratio of 8.5 dB at 0.01% (probability) CCDF:

— Output power: 38 W.

— Power gain: 14 dB.

— Efficiency: 26%.

— IM3: –36 dBc.

— ACPR: –39 dBc.

— Return loss: –12 dB.

I High-reliability, gold-metalization process.

I Hot carrier injection (HCI) induced bias drift of <5%

over 20 years.

I Internally matched.

I High gain, efficiency, and linearity.

I Integrated ESD protection.

I Device can withstand a 10:1 voltage standing wave

ratio (VSWR) at 28 Vdc, 2140 MHz, 180 W output

power pulsed 4 s at 10% duty.

I Large signal impedance parameters available.

Table 1. Thermal Characteristics

Table 2. Absolute Maximum Ratings*

* Stresses in excess of the absolute maximum ratings can cause

permanent damage to the device. These are absolute stress rat-

ings only. Functional operation of the device is not implied at

these or any other conditions in excess of those given in the

operational sections of the data sheet. Exposure to absolute

maximum ratings for extended periods can adversely affect

device reliability.

Table 3. ESD Rating*

* Although electrostatic discharge (ESD) protection circuitry has

been designed into this device, proper precautions must be

taken to avoid exposure to ESD and electrical overstress (EOS)

during all handling, assembly, and test operations. Agere

employs a human-body model (HBM), a machine model (MM),

and a charged-device model (CDM) qualification requirement in

order to determine ESD-susceptibility limits and protection

design evaluation. ESD voltage thresholds are dependent on the

circuit parameters used in each of the models, as defined by

JEDEC's JESD22-A114B (HBM), JESD22-A115A (MM), and

JESD22-C101A (CDM) standards.

Caution: MOS devices are susceptible to damage from elec-

trostatic charge. Reasonable precautions in han-

dling and packaging MOS devices should be

observed.

AGR21180EU (unflanged)

AGR21180EF (flanged)

375D–03, STYLE 1

Parameter

Sym

Value

Unit

Thermal Resistance,

Junction to Case:

AGR21180EU

AGR21180EF

R

θJC

R

θJC

0.35

°C/W

Parameter

Sym

Value

Unit

Drain-source Voltage

VDSS

65

Vdc

Gate-source Voltage

VGS

–0.5, 15

Vdc

Total Dissipation at TC = 25 °C:

AGR21180EU

AGR21180EF

PD

500

W

Derate Above 25

°C:

AGR21180EU

AGR21180EF

—

2.86

W/°C

Operating Junction Tempera-

ture

TJ

200

°C

Storage Temperature Range

TSTG –65, 150

°C

AGR21180E

Minimum (V)

Class

HBM

500

1B

MM

50

A

CDM

1000

4

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AGR21180EU | S BAND, Si, N-CHANNEL, RF POWER, MOSFET |

| AGRA10EU | UHF BAND, Si, N-CHANNEL, RF POWER, MOSFET |

| AGRA10EU | UHF BAND, Si, N-CHANNEL, RF POWER, MOSFET |

| AP4532GM | 5 A, 30 V, 0.05 ohm, 2 CHANNEL, N AND P-CHANNEL, Si, POWER, MOSFET |

| APM2023NUC-TRG | 7 A, 20 V, 0.023 ohm, N-CHANNEL, Si, POWER, MOSFET, TO-252 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AGR21N090EF | 功能描述:射頻MOSFET電源晶體管 RF Transistor RoHS:否 制造商:Freescale Semiconductor 配置:Single 晶體管極性: 頻率:1800 MHz to 2000 MHz 增益:27 dB 輸出功率:100 W 汲極/源極擊穿電壓: 漏極連續(xù)電流: 閘/源擊穿電壓: 最大工作溫度: 封裝 / 箱體:NI-780-4 封裝:Tray |

| AGR26045EF | 功能描述:射頻MOSFET電源晶體管 RF Transistor RoHS:否 制造商:Freescale Semiconductor 配置:Single 晶體管極性: 頻率:1800 MHz to 2000 MHz 增益:27 dB 輸出功率:100 W 汲極/源極擊穿電壓: 漏極連續(xù)電流: 閘/源擊穿電壓: 最大工作溫度: 封裝 / 箱體:NI-780-4 封裝:Tray |

| AGR26125E | 制造商:TRIQUINT 制造商全稱:TriQuint Semiconductor 功能描述:125 W, 2.5 GHz-2.7 GHz, N-Channel E-Mode, Lateral MOSFET |

| AGR26125EF | 功能描述:射頻MOSFET電源晶體管 RF Transistor RoHS:否 制造商:Freescale Semiconductor 配置:Single 晶體管極性: 頻率:1800 MHz to 2000 MHz 增益:27 dB 輸出功率:100 W 汲極/源極擊穿電壓: 漏極連續(xù)電流: 閘/源擊穿電壓: 最大工作溫度: 封裝 / 箱體:NI-780-4 封裝:Tray |

| AGR26125EU | 制造商:TRIQUINT 制造商全稱:TriQuint Semiconductor 功能描述:125 W, 2.5 GHz-2.7 GHz, N-Channel E-Mode, Lateral MOSFET |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。