- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄166131 > AK4641VN (Asahi Kasei Microsystems Co.,Ltd) 16 BIT CODEC WITH BLUETOOTH INTERFACE PDF資料下載

參數(shù)資料

| 型號: | AK4641VN |

| 廠商: | Asahi Kasei Microsystems Co.,Ltd |

| 元件分類: | Codec |

| 英文描述: | 16 BIT CODEC WITH BLUETOOTH INTERFACE |

| 中文描述: | 16位編解碼器與藍牙接口 |

| 文件頁數(shù): | 18/51頁 |

| 文件大小: | 461K |

| 代理商: | AK4641VN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁

ASAHI KASEI

[AK4641]

MS0301-E-00

2004/05

- 25 -

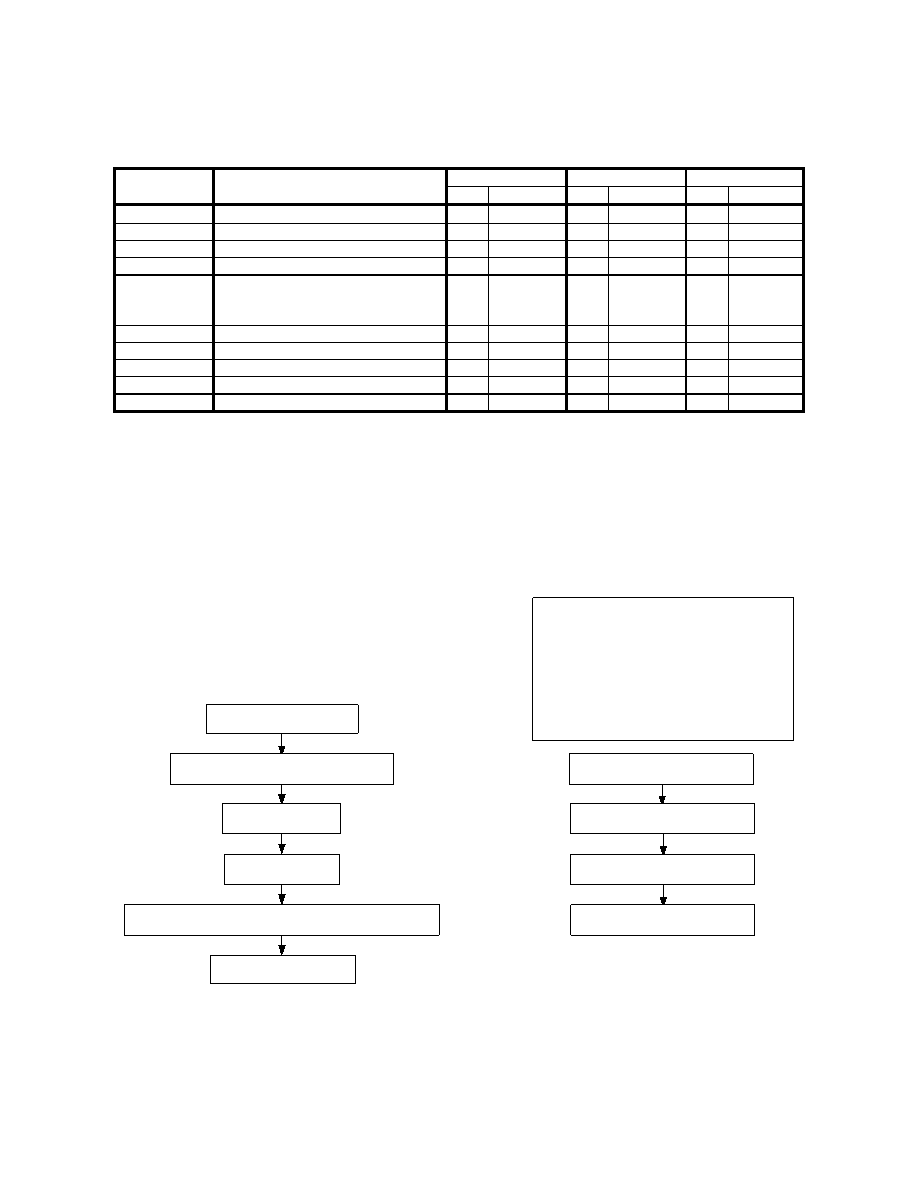

[3] Example of ALC1 Operation

Table 11 shows the examples of the ALC1 setting. In case of this examples, ALC1 operation starts from 0dB.

fs=8kHz

fs=16kHz

fs=44.1kHz

Register Name

Comment

Data

Operation

Data

Operation

Data

Operation

LMTH

Limiter detection Level

1

4dBFS

1

4dBFS

1

4dBFS

LTM1-0

Limiter operation period at ZELM = 1

00

Don’t use

00

Don’t use

00

Don’t use

ZELM

Limiter zero crossing detection

0

Enable

0

Enable

0

Enable

ZTM1-0

Zero crossing timeout period

00

16ms

01

16ms

10

11.6ms

WTM1-0

Recovery waiting period

*WTM1-0 bits should be the same data

as ZTM1-0 bits

00

16ms

01

16ms

10

11.6ms

REF6-0

Maximum gain at recovery operation

47H

+27.5dB

47H

+27.5dB

47H

+27.5dB

IPGA6-0

Gain of IPGA at ALC1 operation Start

10H

0dB

10H

0dB

10H

0dB

LMAT1-0

Limiter ATT Step

00

1 step

00

1 step

00

1 step

RATT

Recovery GAIN Step

0

1 step

0

1 step

0

1 step

ALC1

ALC1 Enable bit

1

Enable

1

Enable

1

Enable

Table 11. Example of the ALC1 setting

The following registers should not be changed during the ALC1 operation. These bits should be changed, after the ALC1

operation is finished by ALC1 bit = “0” or PMMIC bit = “0”.

LTM1-0, LMTH, LMAT1-0, WTM1-0, ZTM1-0, RATT, REF6-0, ZELM bits

IPGA gain at ALC1 operation start can be changed from the default value of IPGA6-0 bits while PMMIC bit is “1” and

ALC1 bit is “0”. When ALC1 bit is changed from “1” to “0”, IPGA holds the last gain value set by ALC1 operation.

Manual Mode

* The value of IPGA should be

the same or smaller than REF’s

WR (ZTM1-0, WTM1-0, LTM1-0)

WR (REF6-0)

WR (IPGA6-0)

ALC1 Operation

WR (ALC1= “1”, LMAT1-0, RATT, LMTH, ZELM)

Example:

Limiter = Zero crossing Enable

Recovery Cycle = 16ms @ fs= 8kHz

Limiter and Recovery Step = 1

Maximum Gain = +27.5dB

Limiter Detection Level =

4dBFS

(1) Addr=08H, Data=00H

(2) Addr=0AH, Data=47H

(4) Addr=09H, Data=21H

(3) Addr=0BH, Data=10H

* ALC1 bit must be set to “1” at more than zero cross time out period

after the value of IPGA is set (see figure 22).

Note : WR : Write

Figure 23. Registers set-up sequence at ALC1 operation

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AK4665AEN | SPECIALTY CONSUMER CIRCUIT, QCC32 |

| AK5368192WP-80 | 8M X 36 FAST PAGE DRAM MODULE, 80 ns, SMA72 |

| AK5385A | 24BIT 192KHZ ADC |

| AK8406A | AK8406A |

| AK8432 | 6CH 10bit 40MSPS】3 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AK4642 | 制造商:AKM 制造商全稱:AKM 功能描述:16-Bit ???£ Stereo CODEC with MIC/HP/SPK-AMP |

| AK4642EN | 制造商:AKM 制造商全稱:AKM 功能描述:Stereo CODEC with MIC/HP/SPK-AMP |

| AK4642VN | 制造商:AKM 制造商全稱:AKM 功能描述:16-Bit ???£ Stereo CODEC with MIC/HP/SPK-AMP |

| AK4643 | 制造商:AKM 制造商全稱:AKM 功能描述:Stereo CODEC with built-in MIC/HP/RCV/SPK amplifier |

| AK4643EN | 制造商:AKM 制造商全稱:AKM 功能描述:Stereo CODEC with MIC/HP/RCV/SPK-AMP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。