- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376485 > AM29SL400CB150WAD (SPANSION LLC) 4 Megabit (512 K x 8-Bit/256 K x 16-Bit) CMOS 1.8 Volt-only Super Low Voltage Flash Memory PDF資料下載

參數(shù)資料

| 型號: | AM29SL400CB150WAD |

| 廠商: | SPANSION LLC |

| 元件分類: | DRAM |

| 英文描述: | 4 Megabit (512 K x 8-Bit/256 K x 16-Bit) CMOS 1.8 Volt-only Super Low Voltage Flash Memory |

| 中文描述: | 256K X 16 FLASH 1.8V PROM, 150 ns, PBGA48 |

| 封裝: | 6 X 8 MM, 0.80 MM PITCH, LEAD FREE, FBGA-48 |

| 文件頁數(shù): | 20/44頁 |

| 文件大小: | 945K |

| 代理商: | AM29SL400CB150WAD |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

18

March 3, 2005

A d v a n c e I n f o r m a t i o n

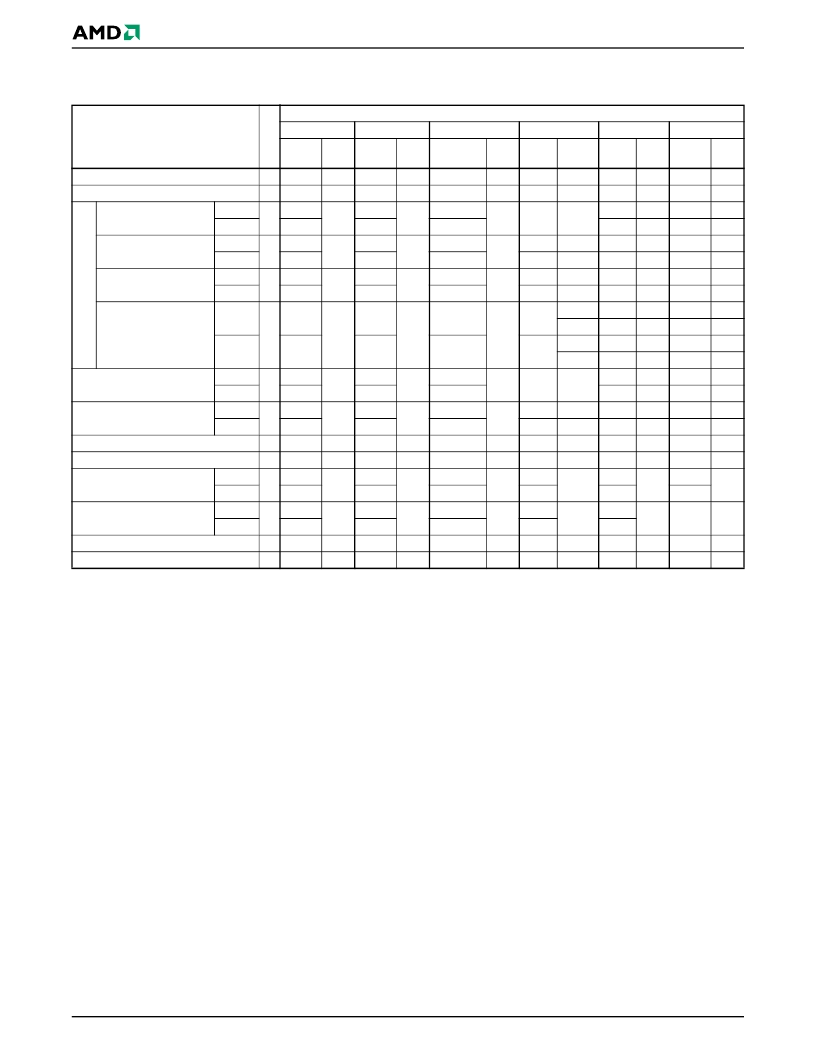

Command Definitions

Table 5.

Am29SL400C Command Definitions

Legend:

X = Don’t care

RA = Address of the memory location to be read.

RD = Data read from location RA during read operation.

PA = Address of the memory location to be programmed. Addresses latch on the falling edge of the WE# or CE# pulse,

whichever happens later.

PD = Data to be programmed at location PA. Data latches on the rising edge of WE# or CE# pulse, whichever happens first.

SA = Address of the sector to be verified (in autoselect mode) or erased. Address bits A17–A12 uniquely select any sector.

Notes:

1.

See Table 1 for description of bus operations.

2.

All values are in hexadecimal.

3.

Except when reading array or autoselect data, all bus

cycles are write operations.

4.

Data bits DQ15–DQ8 are don’t cares for unlock and

command cycles.

5.

Address bits A17–A11 are don’t cares for unlock and

command cycles, unless SA or PA required.

6.

No unlock or command cycles required when reading

array data, unless SA or PA required.

7.

The Reset command is required to return to reading array

data when device is in the autoselect mode, or if DQ5

goes high (while the device is providing status data).

8.

The fourth cycle of the autoselect command sequence is

a read cycle.

9.

The data is 00h for an unprotected sector and 01h for a

protected sector.

See “Autoselect Command

Sequence”

for more information.

10. The Unlock Bypass command is required prior to the

Unlock Bypass Program command.

11. The Unlock Bypass Reset command is required to return

to reading array data when the device is in the unlock

bypass mode.

12. The system may read and program in non-erasing

sectors, or enter the autoselect mode, when in the Erase

Suspend mode. The Erase Suspend command is valid

only during a sector erase operation.

13. The Erase Resume command is valid only during the Erase

Suspend mode.

Write Operation Status

The device provides several bits to determine the sta-

tus of a write operation: DQ2, DQ3, DQ5, DQ6, DQ7,

and RY/BY#.

Table 6 on page 22

and the following

Command

Sequence

(Note 1)

C

Bus Cycles (Notes 2-5)

Third

Dat

a

First

Second

Fourth

Fifth

Sixth

Addr

RA

XXX

555

AAA

555

AAA

555

AAA

Dat

a

RD

F0

Addr

Dat

a

Addr

Addr

Data

Addr

Dat

a

Addr

Dat

a

Read (Note 6)

Reset (Note 7)

1

1

A

Manufacturer ID

Word

Byte

Word

Byte

Word

Byte

4

AA

2AA

555

2AA

555

2AA

555

55

555

AAA

555

AAA

555

AAA

90

X00

01

Device ID,

Top Boot Block

4

AA

55

90

X01

X02

X01

X02

70h

70h

FIh

FIh

XX00

XX01

00

01

Device ID,

Bottom Boot Block

4

AA

55

90

Sector Protect Verify

(Note 9)

Word

4

555

AA

2AA

55

555

90

(SA)

X02

Byte

AAA

555

AAA

(SA)

X04

Program

Word

Byte

Word

Byte

4

555

AAA

555

AAA

XXX

XXX

555

AAA

555

AAA

XXX

XXX

AA

2AA

555

2AA

555

PA

XXX

2AA

555

2AA

555

55

555

AAA

555

AAA

A0

PA

PD

Unlock Bypass

3

AA

55

20

Unlock Bypass Program (Note 10)

Unlock Bypass Reset (Note 11)

2

2

A0

90

PD

00

Chip Erase

Word

Byte

Word

Byte

6

AA

55

555

AAA

555

AAA

80

555

AAA

555

AAA

AA

2AA

555

2AA

555

55

555

AAA

10

Sector Erase

6

AA

55

80

AA

55

SA

30

Erase Suspend (Note 12)

Erase Resume (Note 13)

1

1

B0

30

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM29SL400CT150WAF | CAP 150UF 4V 20% TANT SMD-7343-30 TR-7 |

| AM29SL400CB150WAF | 4 Megabit (512 K x 8-Bit/256 K x 16-Bit) CMOS 1.8 Volt-only Super Low Voltage Flash Memory |

| AM29SL400CT150WAI | 4 Megabit (512 K x 8-Bit/256 K x 16-Bit) CMOS 1.8 Volt-only Super Low Voltage Flash Memory |

| AM29SL400CB150WAI | 4 Megabit (512 K x 8-Bit/256 K x 16-Bit) CMOS 1.8 Volt-only Super Low Voltage Flash Memory |

| AM29SL400CT120EF | 4 Megabit (512 K x 8-Bit/256 K x 16-Bit) CMOS 1.8 Volt-only Super Low Voltage Flash Memory |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM29SL800DB120WCI | 制造商:Spansion 功能描述:FLASH PARALLEL 1.8V 8MBIT 1MX8/512KX16 120NS 48FBGA - Trays |

| AM29SL800DB90WAD | 制造商:Spansion 功能描述: |

| AM29X305ADC | 制造商:Advanced Micro Devices 功能描述:Microprocessor, 8 Bit, 50 Pin, Ceramic, DIP |

| AM2A016 | 制造商:MAG-LITE 功能描述:Bulk |

| AM2A026 | 制造商:MAG-LITE 功能描述:Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。