- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362278 > AM486DE2 Am486DE2 Microprocessor Data Sheet PDF資料下載

參數(shù)資料

| 型號: | AM486DE2 |

| 英文描述: | Am486DE2 Microprocessor Data Sheet |

| 中文描述: | Am486DE2微處理器數(shù)據(jù)表 |

| 文件頁數(shù): | 37/52頁 |

| 文件大小: | 1242K |

| 代理商: | AM486DE2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

Am486DE2 Microprocessor

37

Am486DE2 MICROPROCESSOR FUNCTIONAL DIFFERENCES

The Am486DE2 microprocessor is a new member of the

AMD Am486 family, which also includes the Enhanced

Am486 and the Am486DX microprocessors.

Although the Am486DE2 is based on and compatible

with the Enhanced Am486 microprocessors, it has no

support for write-back cache.

Several important differences exist between the

Am486DE2 and the Am486DX processors:

I

The Am486DE2 ID register contains a different

version signature than the Am486DX. It has the

same ID register as the Enhanced Am486DX2 in

Write-through mode.

I

A burst write feature is available for copy-backs. The

FLUSH pin and WBINVD instruction copy-back all

modified data to external memory prior to issuing the

special bus cycle or reset.

I

The RESET state is invoked either after power up or

after the RESET signal is applied according to the

standard Am486DX microprocessor specification.

I

After reset, the STATUS bits of all lines are set to 0.

The LRU bits of each set are placed in a starting

state.

In addition, the differences in the processors are high-

lighted in Table 12.

Am486DE2 MICROPROCESSOR IDENTIFICATION

The Am486DE2 microprocessor supports two standard

methods for identifying the CPU in a system. The report-

ed values are dynamically assigned based on the CPU

type and the status of the WB/WT pin input at RESET.

DX Register at RESET

The DX register always contains a component identifier

at the conclusion of RESET. The upper byte of DX (DH)

contains 04 and the lower byte of DX (DL) contains a

CPU type/stepping identifier (see Table 13).

CPUID Instruction

The Am486DE2 implements a new instruction that

makes information available to software about the

family, model, and stepping of the microprocessor on

which it is executing. Support of this instruction is

indicated by the presence of a user-modifiable bit in

position EFLAGS.21, referred to as the EFLAGS.ID bit.

This bit is reset to zero at device reset (RESET or

SRESET) for compatibility with existing processor

designs.

CPUID Timing

CPUID execution timing depends on the selected EAX

parameter values (see Table 14).

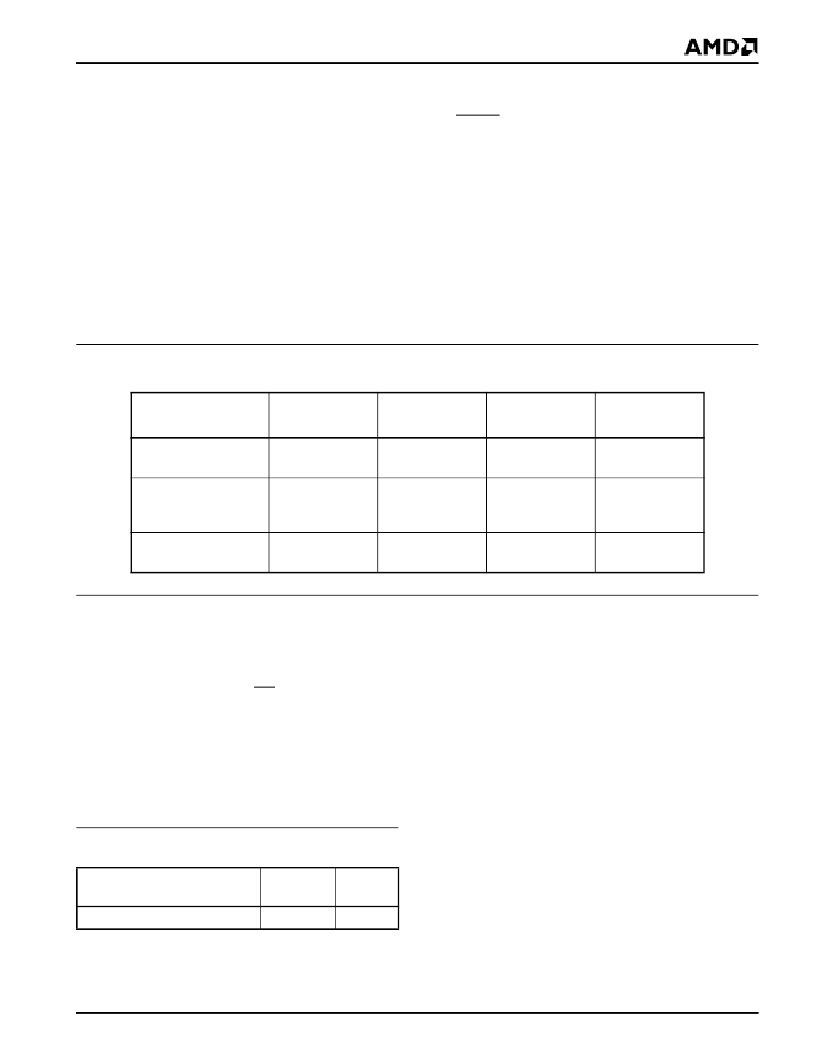

Table 12. Am486DE2 Microprocessor Functional Differences

Processor

Cache

Clock

Major

Enhancements

Package

Am486DX2-66

8 Kbyte,

Write-through

1x, 2x

168-Pin PGA

Enhanced

Am486DX2-66

8-Kbyte,

Write-through/

Write-back

2x, 3x

SMI, write-back

168-Pin PGA

Am486DE2-66

8-Kbyte,

Write-through

2x

SMI

168-Pin PGA,

208-Lead SQFP

Table 13. CPU ID Codes

CPU Type and Cache Mode

Component

ID (DH)

Revision

ID (DL)

DE2 in Write-through mode

04

3x

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM486DX | Am486DX - Am486DX Block Diagram |

| AM486DXPGA | Am486DX PGA - Am486DX PGA Package Temperature Comparisons |

| AM486DXSQFP | 70NS, PLCC, IND TEMP(EEPROM) |

| AM486 | Am486 Microprocessor Software User's Manual? 4.40MB (PDF) |

| AM49DL3208G | Am49DL3208G - Stacked Multi-Chip Package (MCP) Flash Memory and pSRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM486DE2-66V8TGC | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:8-Kbyte Write-Through Embedded Microprocessor |

| AM486DE2-66V8THC | 制造商:Advanced Micro Devices 功能描述:Microprocessor, 32 Bit, 208 Pin, Plastic, QFP |

| AM486DX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Am486DX - Am486DX Block Diagram |

| AM486DX/DX2 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Am486DX/DX2 Hardware Reference Manual |

| AM486DX2 | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:Am5X86⑩ Microprocessor Family |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。