- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366550 > AM79C90 (Advanced Micro Devices, Inc.) CMOS Local Area Network Controller for Ethernet (C-LANCE) PDF資料下載

參數(shù)資料

| 型號: | AM79C90 |

| 廠商: | Advanced Micro Devices, Inc. |

| 英文描述: | CMOS Local Area Network Controller for Ethernet (C-LANCE) |

| 中文描述: | 的CMOS局域網(wǎng)控制器(丙應聘以太網(wǎng)) |

| 文件頁數(shù): | 26/62頁 |

| 文件大小: | 437K |

| 代理商: | AM79C90 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁

AMD

P R E L I M I N A R Y

26

Am79C90

The Broadcast address, which consists of all ones is a

special multicast address. Packets addressed to the

broadcast address must be received by all nodes. Since

broadcast packets are usually more common than other

multicast packets, the broadcast address should be the

first address in the multicast address list.

The Broadcast address does not go through the Logical

Address Filter and is always enabled. If the Logical Ad-

dress Filter is loaded with all zeroes, all incoming logical

addresses except broadcast will be rejected. The multi-

cast addressing in external loopback is operational only

when DTCR in the mode register is set to 1.

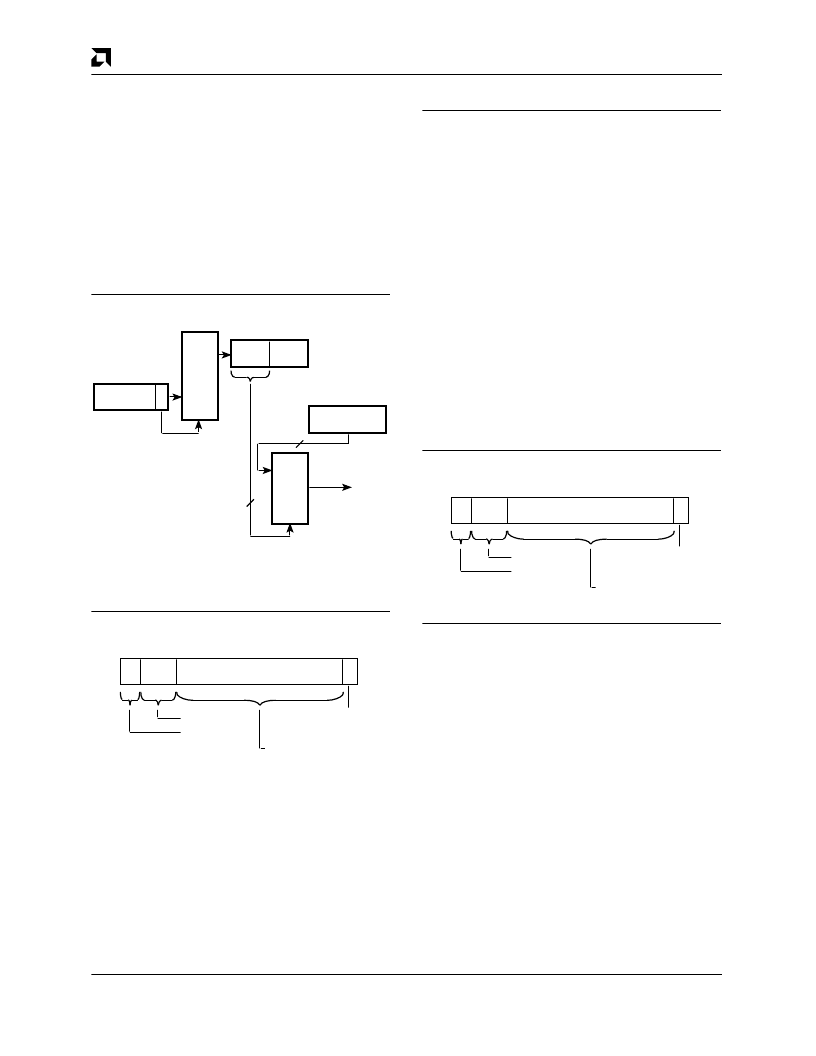

Destination

Address

47

1 0

CRC

Gen

32-Bit Resultant CRC

31

26

0

Logical Address

Filter

63

0

“1”

Enable

64

MUX

Select

Match*

6

*Match - 1, the packet is accepted

Match - 0, the packet is rejected

17881B-22

Figure 7. Logical Address Filter Operation

Receive Descriptor Ring Pointer

31

2 0

17881B-23

2928 24 23

3

RES

RLEN

000 ‘(Quadword

Boundary)’

RDRA (23:03)

Bit

Name

Description

31:29

RLEN

RECEIVE RING LENGTH is the

number of entries in the receive ring

expressed as a power of two.

RLEN

Number of Entries

0

1

2

3

4

5

6

7

RESERVED. Read as zeroes. Write

as zeroes.

RECEIVE DESCRIPTOR RING AD-

DRESS is the base address (lowest

address) of the Receive Descriptor

Ring.

MUST BE ZEROES. These bits are

RDRA (02:00) and must be zeroes

because the Receive Ring is aligned

on a quadword boundary.

1

2

4

8

16

32

64

128

28:24

RES

23:03

RDRA

02:00

Transmit Descriptor Ring Pointer

31

2 0

17881B-24

2928 24 23

3

RES

TLEN

000 ‘(Quadword

Boundary)’

TDRA (23:03)

31:29

TLEN

TRANSMIT RING LENGTH is the

number of entries in the Transmit

Ring expressed as a power of two.

TLEN

Number of Entries

0

1

2

3

4

5

6

7

RESERVED. Read as zeroes. Write

as zeroes.

TRANSMIT DESCRIPTOR RING

ADDRESS is the base address (low-

est address) of the Transmit De-

scriptor Ring.

MUST BE ZEROES. These bits are

TDRA (02:00) and must be zeroes

because the Transmit Ring is

aligned on a quadword boundary.

1

2

4

8

16

32

64

128

28:24

RES

23:03

TDRA

02:00

相關PDF資料 |

PDF描述 |

|---|---|

| AM79C90JC | CMOS Local Area Network Controller for Ethernet (C-LANCE) |

| AM79C90JCTR | KPTC6CG10-6P |

| AM79C90PC | CMOS Local Area Network Controller for Ethernet (C-LANCE) |

| AM79C90PCTR | CMOS Local Area Network Controller for Ethernet (C-LANCE) |

| AM79C930 | PCnet-Mobile Single-Chip Wireless LAN Media Access Controller |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C900 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| AM79C900AJC | 制造商:Advanced Micro Devices 功能描述: |

| AM79C900JC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN Node Controller |

| AM79C901 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:AMD’s Am79C901 HomePNA-Compliant Device with Motorola’s MC68360. MPC860. MPC850. and MPC8260? - (PDF) |

發(fā)布緊急采購,3分鐘左右您將得到回復。