- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366550 > AM79C90JC (ADVANCED MICRO DEVICES INC) CMOS Local Area Network Controller for Ethernet (C-LANCE) PDF資料下載

參數(shù)資料

| 型號: | AM79C90JC |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | CMOS Local Area Network Controller for Ethernet (C-LANCE) |

| 中文描述: | 1 CHANNEL(S), LOCAL AREA NETWORK CONTROLLER, PQCC68 |

| 封裝: | PLASTIC, LCC-68 |

| 文件頁數(shù): | 30/62頁 |

| 文件大小: | 437K |

| 代理商: | AM79C90JC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁

AMD

P R E L I M I N A R Y

30

Am79C90

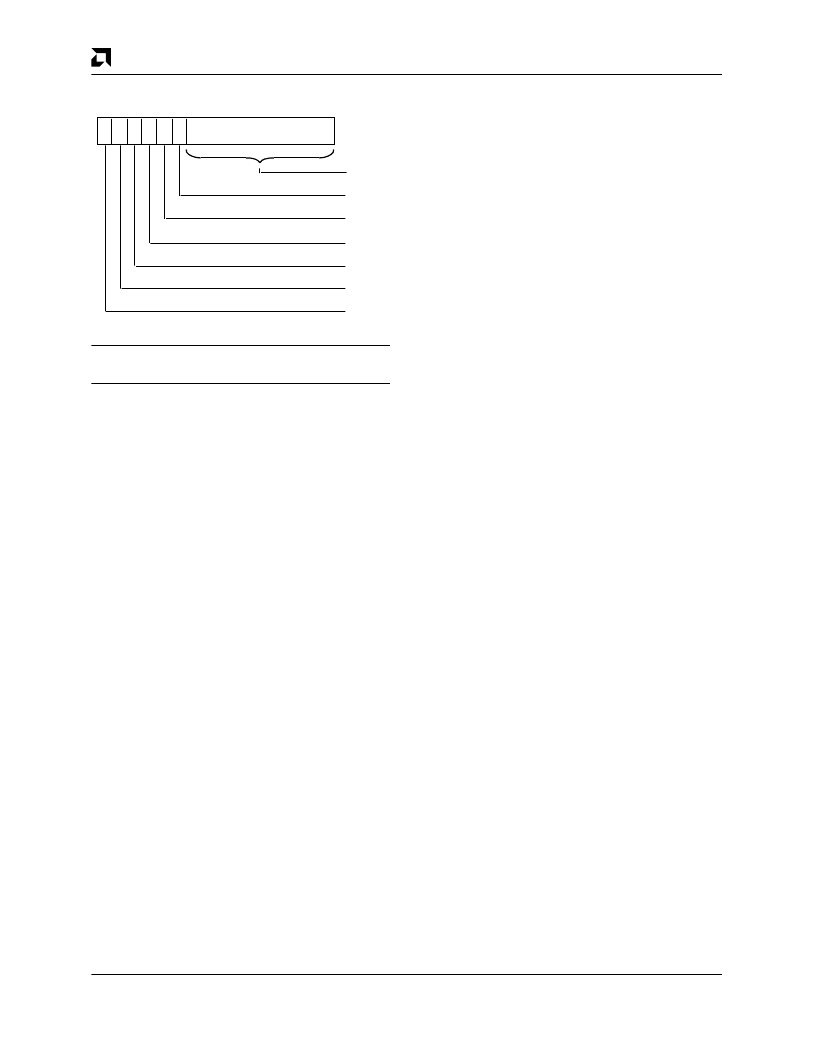

Transmit Message Descriptor 3 (TMD3)

RTRY

LCAR

LCOL

RES

UFLO

BUFF

15

10 9

0

TDR

17881B-32

Bit

Name

Description

15

BUFF

BUFFER ERROR is set by the

C-LANCE during transmission when

the C-LANCE does not find the ENP

flag in the current buffer and does

not own the next buffer. This can oc-

cur in either of two ways: either the

OWN bit of the next buffer is zero, or

Transmit FIFO underflow occurred

before the C-LANCE has performed

a lookahead poll of the next transmit

descriptor. BUFF is set by the

C-LANCE and cleared by the host.

BUFF error will turn off the transmit-

ter (CSR

0

, TXON = 0).

If a Buffer Error occurs, an Underflow

Error will also occur. BUFF error is

not valid when LCOL or RTRY error

is set during TX data chaining.

UNDERFLOW ERROR indicates

that the transmitter has truncated a

message due to data late from mem-

ory. UFLO indicates that the Trans-

mit FIFO has emptied before the end

of the packet was reached.

Upon UFLO error, transmitter is

turned off (CSR

0

, TXON = 0).

RESERVED bit. The C-LANCE will

write this bit with a “0.”

LATE COLLISION indicates that a

collision has occurred after the slot

time of the channel has elapsed. The

C-LANCE does not retry on late

collisions.

LOSS OF CARRIER is set when the

carrier

input

(RENA)

C-LANCE goes false during a

C-LANCE-initiated

The C-LANCE does not retry upon

loss of carrier. It will continue to

transmit the whole packet until done.

LCAR is not valid in INTERNAL

LOOPBACK MODE.

14

UFLO

13

RES

12

LCOL

11

LCAR

to

the

transmission.

10

RTRY

RETRY ERROR indicates that the

transmitter has failed in 16 attempts

to successfully transmit a message

due to repeated collisions on the me-

dium. If DRTY = 1 in the MODE reg-

ister, RTRY will set after 1 failed

transmission attempt.

TIME DOMAIN REFLECTOMETRY

reflects the state of an internal C-

LANCE counter that counts from the

start of a transmission to the occur-

rence of a collision. This value is

useful in determining the approxi-

mate distance to a cable fault. The

TDR value is written by the

C-LANCE and is valid only if RTRY

isset.

09:00

TDR

Ring Access Mechanism in the C-LANCE

Once the C-LANCE is initialized through the initializa-

tion block and started, the CPU and the C-LANCE com-

municate via transmit and receive rings, for packet

transmission and reception.

There are 2 sets of RAM locations (four 16-bit register

per set, corresponding to the 4 entries in each descrip-

tor) in the C-LANCE. The first set points to the current

buffer, and they are the working registers which are

used for transferring the data for the packet. The second

set contains the pointers to the next buffer in the ring

which the C-LANCE obtained from the lookahead

operation.

There are three types of ring access in the C-LANCE.

The first type is when the C-LANCE polls the rings to

own a buffer. The second type is when the buffers are

data chained. The C-LANCE does a lookahead opera-

tion between the time that it is transferring data to/from

the Transmit/Receive FIFOs; this lookahead is done

only once. The third type is when the C-LANCE tries to

own the next descriptor in the ring when it clears the

OWN bit for the current buffer.

Transmit Ring Buffer Management

When there is no Ethernet activity, the C-LANCE will

automatically poll the transmit ring in the memory once it

has started (CSR0, STRT = 1). This polling occurs every

1.6 ms, (CSR0 TDMD bit = 0) and consists of reading

the status word of the transmit descriptor, TMD1, until

the C-LANCE owns the descriptor. The C-LANCE will

read TMD0 and TMD2 to get the rest of the buffer ad-

dress and the buffer byte count when it owns the de-

scriptor. Each of these memory reads is done

separately with a new arbitration cycle for each transfer.

If the transmit buffers are data chained (current buffer

ENP = 0), the C-LANCE will look ahead to the next de-

scriptor in the ring while transferring the current buffer

into the Transmit FIFO (see Figure 8-1). The C-LANCE

does this lookahead only once. If it does not own the

next transmit Descriptor Table Entry (DTE) (2nd TX ring

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C90JCTR | KPTC6CG10-6P |

| AM79C90PC | CMOS Local Area Network Controller for Ethernet (C-LANCE) |

| AM79C90PCTR | CMOS Local Area Network Controller for Ethernet (C-LANCE) |

| AM79C930 | PCnet-Mobile Single-Chip Wireless LAN Media Access Controller |

| AM79C930VCW | PCnet-Mobile Single-Chip Wireless LAN Media Access Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C90JC-G | 制造商:Rochester Electronics LLC 功能描述: |

| AM79C90JCTR | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:CMOS Local Area Network Controller for Ethernet (C-LANCE) |

| AM79C90PC | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:CMOS Local Area Network Controller for Ethernet (C-LANCE) |

| AM79C90PCB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN Node Controller |

| AM79C90PCTR | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:CMOS Local Area Network Controller for Ethernet (C-LANCE) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。