- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄362442 > AS4C256K16F0-35TC x16 Fast Page Mode DRAM PDF資料下載

參數(shù)資料

| 型號(hào): | AS4C256K16F0-35TC |

| 英文描述: | x16 Fast Page Mode DRAM |

| 中文描述: | x16快速頁(yè)面模式的DRAM |

| 文件頁(yè)數(shù): | 6/25頁(yè) |

| 文件大?。?/td> | 521K |

| 代理商: | AS4C256K16F0-35TC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)

AS4C256K16FO

4/11/01;

V.0.9.1

Alliance Semiconductor

P. 6 of 25

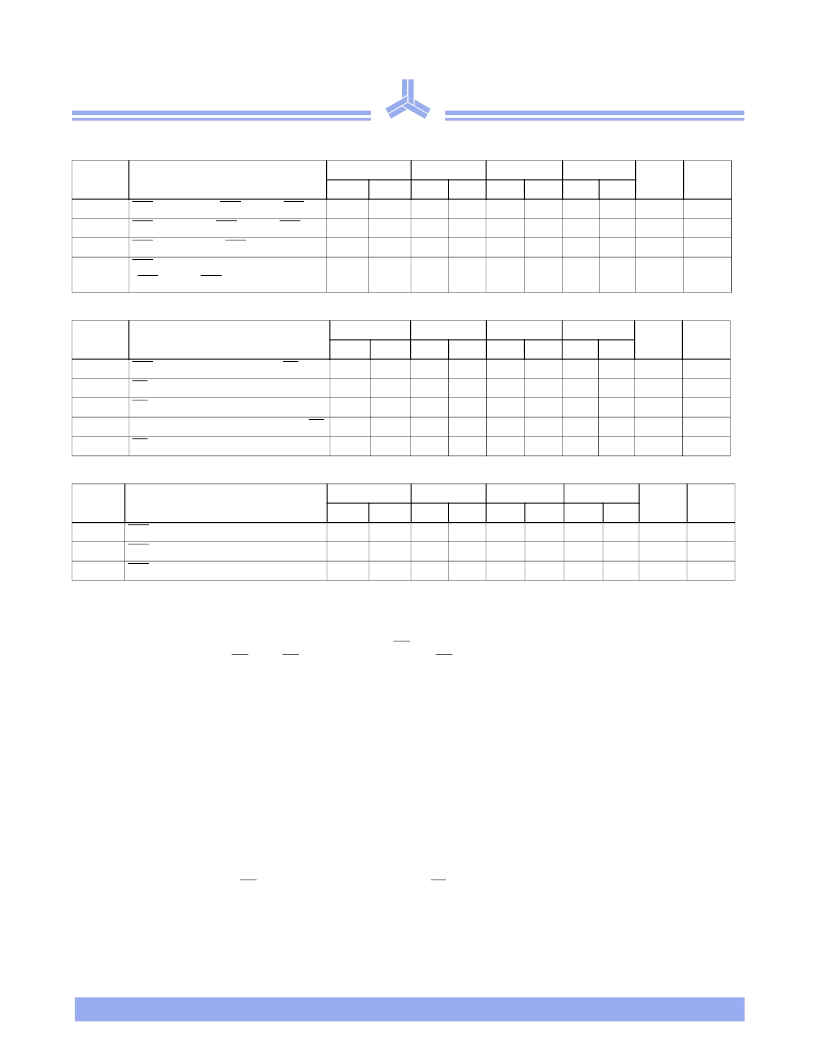

Refresh cycle

Standard

Symbol

t

CSR

t

CHR

t

RPC

(V

CC

= 5V ± 10%, GND = 0V, T

a

= 0

°

C to +70

°

C)

–30

–35

Max

Min

Max

Min

Max

–

10

–

10

–

–

7

–

8

–

–

0

–

0

–

Output enable

Standard

Symbol

t

ROH

t

OEA

t

OED

t

OEZ

t

OEH

(V

CC

= 5V ± 10%, GND = 0V, T

a

= 0

°

C to +70

°

C

)

–30

–35

Max

Min

Max

Min

Max

–

5

–

5

–

8

–

10

–

10

–

5

–

5

–

6

–

8

–

8

–

8

–

8

–

Self refresh cycle

Standard

Symbol

t

RASS

t

RPS

t

CHS

(V

CC

= 5V ± 10%, GND = 0V, T

a

= 0

°

C to +70

°

C

)

–30

–35

Max

Min

Max

Min

Max

–

100K

–

100K

–

–

85

–

85

–

–

30

–

30

–

Notes

1

2

3

I

CC1

, I

CC3

, I

CC4

, and I

CC6

depend on cycle rate.

I

CC1

and I

CC4

depend on output loading. Specified values are obtained with the output open.

An initial pause of 200

μ

s is required after power-up followed by any 8 RAS cycles before proper device operation is achieved. In the case of an internal

refresh counter, a minimum of 8 CAS-before-RAS initialization cycles instead of 8 RAS cycles are required. 8 initialization cycles are required after extended

periods of bias without clocks (greater than 8 ms).

AC characteristics assume t

T

= 5 ns. All AC parameters are measured with a load equivalent to two TTL loads and 100 pF, V

IL

(min)

≥

GND and V

IH

(max)

≤

V

CC

.

V

IH

(min) and V

IL

(max) are reference levels for measuring timing of input signals. Transition times are measured between V

IH

and V

IL

.

Operation within the t

RCD

(max) limit insures that t

RAC

(max) can be met. t

RCD

(max) is specified as a reference point only. If t

RCD

is greater than the speci-

fied t

RCD

(max) limit, then access time is controlled exclusively by t

CAC

.

Operation within the t

RAD

(max) limit insures that t

RAC

(max) can be met. t

RAD

(max) is specified as a reference point only. If t

RAD

is greater than the speci-

fied t

RAD

(max) limit, then access time is controlled exclusively by t

AA

.

Assumes three state test load (5 pF and a 380

Thevenin equivalent).

Either t

RCH

or t

RRH

must be satisfied for a read cycle.

10 t

OFF

(max) defines the time at which the output achieves the open circuit condition; it is not referenced to output voltage levels.

11 t

WCS

, t

WCH

, t

RWD

, t

CWD

and t

AWD

are not restrictive operating parameters. They are included in the datasheet as electrical characteristics only. If t

WS

≥

t

WS

(min) and t

WH

≥

t

WH

(min), the cycle is an early write cycle and data out pins will remain open circuit, high impedance, throughout the cycle. If t

RWD

≥

t

RWD

(min), t

CWD

≥

t

CWD

(min) and t

AWD

≥

t

AWD

(min), the cycle is a read-write cycle and the data out will contain data read from the selected cell. If

neither of the above conditions is satisfied, the condition of the data out at access time is indeterminate.

12 These parameters are referenced to CAS leading edge in early write cycles and to WE leading edge in read-write cycles.

13 Access time is determined by the longest of t

CAA

or t

CAC

or t

CAP

.

14 t

ASC

≥

t

CP

to achieve t

PC

(min) and t

CAP

(max) values.

15 These parameters are sampled, but not 100% tested.

4

5

6

7

8

9

Parameter

–25

–50

Unit

ns

ns

ns

Notes

3

3

Min

10

7

0

Min

10

10

0

Max

–

–

–

CAS setup time (CAS-before-RAS)

CAS hold time (CAS-before-RAS)

RAS precharge to CAS hold time

CAS precharge time

(CAS-before-RAS counter test)

t

CPT

8

–

8

–

8

–

8

–

ns

Parameter

–25

–50

Unit

ns

ns

ns

ns

ns

Notes

Min

5

–

5

–

5

Min

5

–

8

–

8

Max

–

10

–

8

–

RAS hold time referenced to OE

OE access time

OE to data delay

Output buffer turnoff delay from OE

OE command hold time

8

Parameter

–25

–50

Unit

ns

ns

ns

Notes

Min

100K

85

30

Min

100K

85

30

Max

–

–

–

RAS pulse width (CBR self refresh)

RAS precharge time (CBR self refresh)

CAS hold time (CBR self refresh)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AS4C4M4 | 16384Kbits 4M x 4 Replacement with DSCC 5962-n/a | DRAM |

| AS4C4M4E0-70JC | x4 EDO Page Mode DRAM |

| AS4C4M4E1-50JC | x4 EDO Page Mode DRAM |

| AS4C4M4E1-50JI | x4 EDO Page Mode DRAM |

| AS4C4M4E1-50TC | x4 EDO Page Mode DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AS4C256K16F0-35TI | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:x16 Fast Page Mode DRAM |

| AS4C256K16F0-50JC | 制造商:ALSC 制造商全稱(chēng):Alliance Semiconductor Corporation 功能描述:5V 256K X 16 CMOS DRAM (Fast Page Mode) |

| AS4C256K16F0-50JI | 制造商:ALSC 制造商全稱(chēng):Alliance Semiconductor Corporation 功能描述:5V 256K X 16 CMOS DRAM (Fast Page Mode) |

| AS4C256K16F0-50TC | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:x16 Fast Page Mode DRAM |

| AS4C256K16F0-50TI | 制造商:ALSC 制造商全稱(chēng):Alliance Semiconductor Corporation 功能描述:5V 256K X 16 CMOS DRAM (Fast Page Mode) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。