- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379681 > AS5C1008-15 (Austin Semiconductor, Inc) 128K x 8 SRAM RUGGEDIZED PLASTIC HIGH SPEED SRAM PDF資料下載

參數(shù)資料

| 型號: | AS5C1008-15 |

| 廠商: | Austin Semiconductor, Inc |

| 英文描述: | 128K x 8 SRAM RUGGEDIZED PLASTIC HIGH SPEED SRAM |

| 中文描述: | 128K的× 8的SRAM耐用塑料高速SRAM |

| 文件頁數(shù): | 3/9頁 |

| 文件大?。?/td> | 109K |

| 代理商: | AS5C1008-15 |

SRAM

AS5C1008

Austin Semiconductor, Inc.

AS5C1008

Rev. 3.5 1/01

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

3

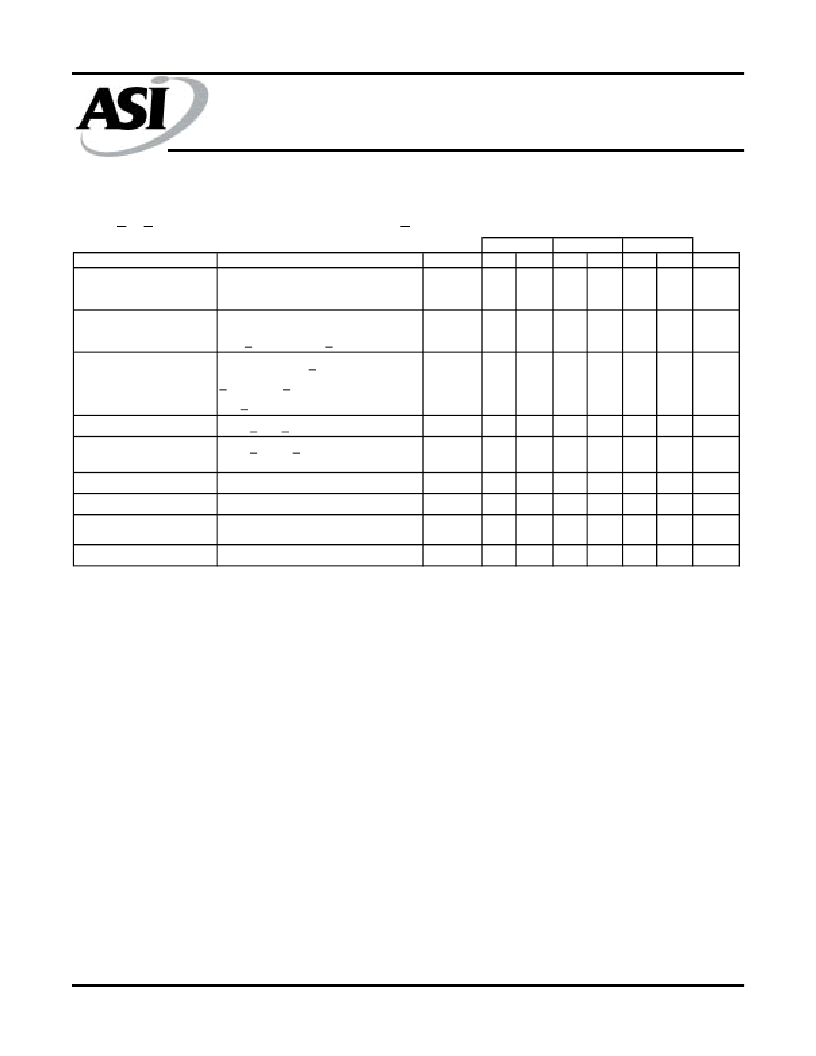

PARAMETER

CONDITIONS

SYMBOL MIN

MAX MIN MAX MIN MAX UNITS

Dynamic Operating

Current

Vcc=MAX, I

OUT

= 0mA,

CE

1

= V

IL

and CE

2

= V

IH

, f = fmax

Vcc=MAX, V

IN

= V

IH

or V

IL

,

CE\

1

> V

IH

and CE

2

> V

IL

, f = fmax

I

CC1

180

150

140

mA

TTL Standby Current -

TTL Inputs

I

SB1

90

75

70

mA

CMOS Standby Current -

CMOS Inputs

Vcc=MAX, CE\

1

> Vcc -0.2V, or CE

2

< 0.2V, V

IN

> Vcc -0.2V and

V

IN

< 0.2V, f = 0

GND < V

IN

< Vcc

GND < V

OUT

< Vcc

Output Disabled

Vcc = MIN, I

OH

= -4.0 mA

Vcc = MIN, I

OL

= 8.0 mA

I

SB2

10

10

10

mA

Input Leakage Current

I

LI

-10

10

-10

10

-10

10

μ

A

Output Leakage Current

I

LO

-10

10

-10

10

-10

10

μ

A

Output High Voltage

V

OH

V

OL

2.4

2.4

2.4

V

Output Low Voltage

0.4

Vcc

+0.5

0.8

0.4

Vcc

+0.5

0.8

0.4

Vcc

+0.5

0.8

V

Input High Voltage

V

IH

2.2

2.2

2.2

V

Input Low Voltage

V

IL

-0.5

-0.5

-0.5

V

-15

-20

-25

ELECTRICAL CHARACTERISTICS AND RECOMMENDED DC OPERATING CONDITIONS

(-55

o

C<T

A

<+125

o

C or -40

o

C to +85

o

C; Vcc = 5V+10%)

PIN DESCRIPTIONS

A0 - A16: Address Inputs

These 17 address inputs select one of the 131,072 8-bit words in

the RAM.

CE\

1

: Chip Enable 1 Input

CE\

1

is asserted LOW to read from or write to the device. If Chip

Enable 1 is deasserted, the device is deselected and is in standby

power mode. The I/O pins will be in the high-impedance state

when the device is deselected.

CE

2

: Chip Enable 2 Input

CE

2

is asserted HIGH to read from or write to the device. If Chip

Enable 2 is deasserted, the device is deselected and is in standby

power mode. The I/O pins will be in the high-impedance state

when the device is deselected.

OE\: Output Enable Input

The Output Enable Input is asserted LOW. If asserted LOW

while CE\

1

is asserted (LOW) and CE

2

is asserted (HIGH) and

WE\ is deasserted (HIGH), data from the SRAM will be present

on the I/O pins. The I/O pins will be in the high-impedance

state when OE\ is deasserted.

WE\: Write Enable Input

The Write Enable input is asserted LOW and controls read and

write operations. When CE\

1

and WE\ are both asserted (LOW)

and CE

2

is asserted (HIGH) input data present on the I/O pins

will be written into the selected memory location.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AS5C512K8ECJ-25 | µP-Compatible 14-Bit CMOS DAC; Package: CERDIP GLASS SEAL; No of Pins: 20; Temperature Range: Industrial |

| AS5C512K8 | 512K x 8 SRAM HIGH SPEED SRAM with REVOLUTIONARY PINOUT |

| AS5C512K8DJ | 512K x 8 SRAM HIGH SPEED SRAM with REVOLUTIONARY PINOUT |

| AS5C512K8EC | 512K x 8 SRAM HIGH SPEED SRAM with REVOLUTIONARY PINOUT |

| AS5C512K8F-45 | 512K x 8 SRAM HIGH SPEED SRAM with REVOLUTIONARY PINOUT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AS5C1008-20 | 制造商:AUSTIN 制造商全稱:Austin Semiconductor 功能描述:128K x 8 SRAM RUGGEDIZED PLASTIC HIGH SPEED SRAM |

| AS5C1008-25 | 制造商:AUSTIN 制造商全稱:Austin Semiconductor 功能描述:128K x 8 SRAM RUGGEDIZED PLASTIC HIGH SPEED SRAM |

| AS5C1008DJ-15/IT | 制造商:Micross Components 功能描述:SRAM, 1MB - Rail/Tube |

| AS5C1008DJ-15/XT | 制造商:Micross Components 功能描述:SRAM, 1MB - Rail/Tube |

| AS5C1008DJ-20/IT | 制造商:Micross Components, Inc. 功能描述:SRAM, 1MB - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。