- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄295111 > AT40K40LV-3EQC (ATMEL CORP) FPGA, 2304 CLBS, 40000 GATES, PQFP240 PDF資料下載

參數(shù)資料

| 型號(hào): | AT40K40LV-3EQC |

| 廠商: | ATMEL CORP |

| 元件分類(lèi): | FPGA |

| 英文描述: | FPGA, 2304 CLBS, 40000 GATES, PQFP240 |

| 封裝: | PLASTIC, QFP-240 |

| 文件頁(yè)數(shù): | 20/67頁(yè) |

| 文件大小: | 1589K |

| 代理商: | AT40K40LV-3EQC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)

27

AT40K/AT40KLV Series FPGA

0896C–FPGA–04/02

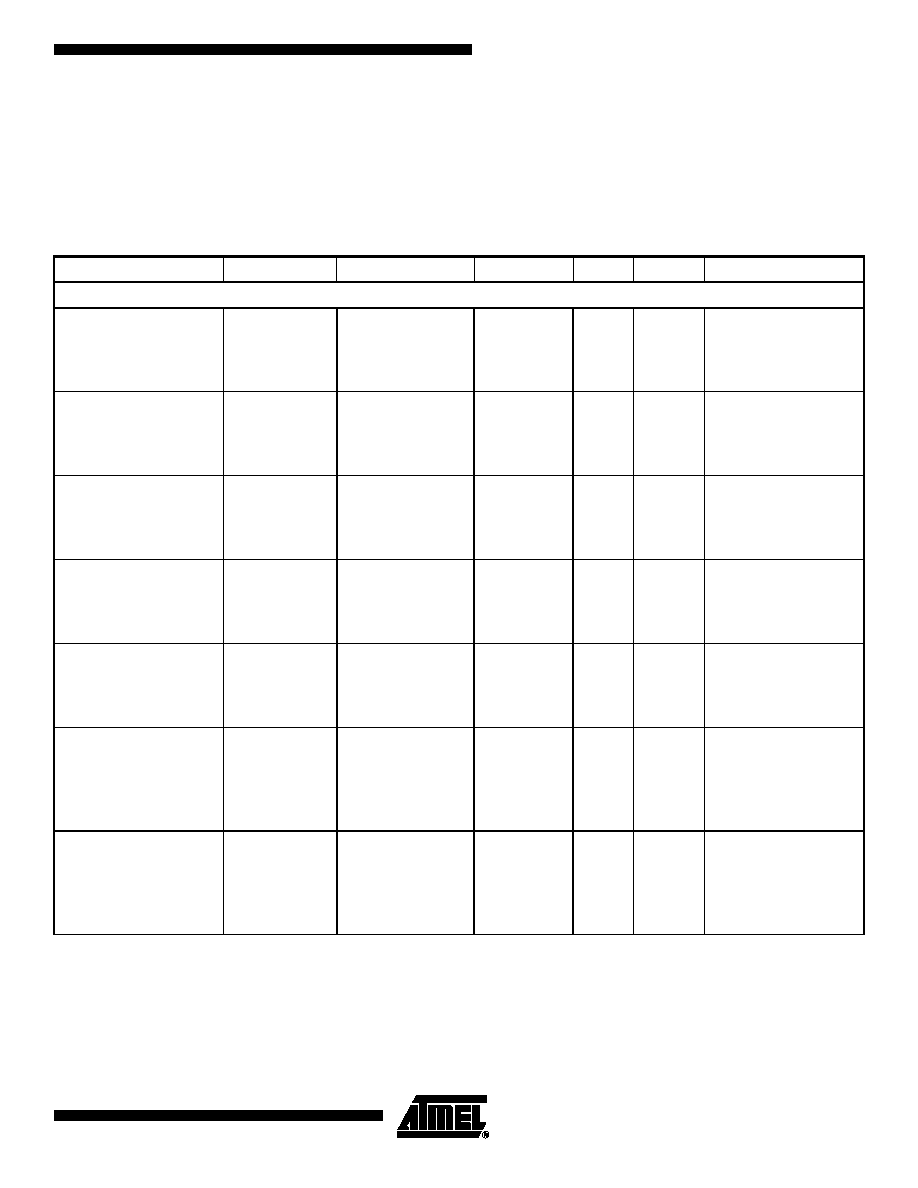

AC Timing Characteristics – 5V Operation AT40K

Delays are based on fixed loads and are described in the notes.

Maximum times based on worst case: VCC = 4.75V, temperature = 70°C

Minimum times based on best case: VCC = 5.25V, temperature = 0°C

Maximum delays are the average of tPDLH and tPDHL.

Clocks and Reset Input buffers are measured from a V

IH of 1.5V at the input pad to the internal VIH of 50% of VCC.

Maximum times for clock input buffers and internal drivers are measured for rising edge delays only.

Cell Function

Parameter

Path

Device

-2

Units

Notes

Global Clocks and Set/Reset

GCLK Input Buffer

t

PD (Maximum)

pad -> clock

AT40K05

AT40K10

AT40K20

AT40K40

1.1

1.2

1.4

ns

Rising edge clock

FCLK Input Buffer

t

PD (Maximum)

pad -> clock

AT40K05

AT40K10

AT40K20

AT40K40

0.7

0.8

ns

Rising edge clock

Clock Column Driver

tPD (Maximum)

clock -> colclk

AT40K05

AT40K10

AT40K20

AT40K40

0.8

0.9

1.0

1.1

ns

Rising edge clock

Clock Sector Driver

t

PD (Maximum)

colclk -> secclk

AT40K05

AT40K10

AT40K20

AT40K40

0.5

ns

Rising edge clock

GSRN Input Buffer

tPD (Maximum)

pad -> GSRN

AT40K05

AT40K10

AT40K20

AT40K40

3.0

3.7

4.3

5.6

ns

From any pad to Global

Set/Reset network

Global Clock to Output

tPD (Maximum)

clock pad -> out

AT40K05

AT40K10

AT40K20

AT40K40

8.3

8.4

8.6

8.8

ns

Rising edge clock

Fully loaded clock tree

Rising edge DFF

20 mA output buffer

50 pf pin load

Fast Clock to Output

t

PD (Maximum)

clock pad -> out

AT40K05

AT40K10

AT40K20

AT40K40

7.9

8.0

8.1

8.3

ns

Rising edge clock

Fully loaded clock tree

Rising edge DFF

20 mA output buffer

50 pf pin load

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AT40K40LV-3FQC | FPGA, 2304 CLBS, 40000 GATES, PQFP304 |

| AT40KEL040KW1SB | FPGA, 2304 CLBS, 50000 GATES, PQFP160 |

| AT40KEL040KZ1SB | FPGA, 2304 CLBS, 50000 GATES, PQFP256 |

| AT89C2051-12SCT/R | 8-BIT, FLASH, 12 MHz, MICROCONTROLLER, PDSO20 |

| AT89C51-24JCT/R | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PQCC44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AT40K40LV-3EQI | 功能描述:IC FPGA 3.3V 2304 CELL 240PQFP RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:AT40K/KLV 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標(biāo)準(zhǔn)包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計(jì):3200 輸入/輸出數(shù):80 門(mén)數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類(lèi)型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應(yīng)商設(shè)備封裝:120-CPGA(34.55x34.55) |

| AT40K40LV-3FQC | 制造商:Atmel Corporation 功能描述:FPGA 50K GATES 2304 CELLS COMM 0.6UM 3.3V 304PQFP - Trays |

| AT40K40LV-3FQI | 功能描述:IC FPGA 3.3V 2304 CELL 304PQFP RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:AT40K/KLV 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標(biāo)準(zhǔn)包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計(jì):3200 輸入/輸出數(shù):80 門(mén)數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類(lèi)型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應(yīng)商設(shè)備封裝:120-CPGA(34.55x34.55) |

| AT40KAL | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:AT40KAL Preliminary [Updated 6/03. 38 Pages] |

| AT40KAL040KW1M | 制造商:ATMEL 制造商全稱(chēng):ATMEL Corporation 功能描述:Military Reprogrammable FPGAs with FreeRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。