- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1904 > ATF1504BE-5AX100 (Atmel)IC CPLD 64MC 1.8V 100-TQFP PDF資料下載

參數(shù)資料

| 型號: | ATF1504BE-5AX100 |

| 廠商: | Atmel |

| 文件頁數(shù): | 10/30頁 |

| 文件大小: | 0K |

| 描述: | IC CPLD 64MC 1.8V 100-TQFP |

| 標準包裝: | 90 |

| 系列: | ATF15xx |

| 可編程類型: | 系統(tǒng)內(nèi)可編程(最少 10,000 次編程/擦除循環(huán)) |

| 最大延遲時間 tpd(1): | 7.0ns |

| 電壓電源 - 內(nèi)部: | 1.7 V ~ 1.9 V |

| 宏單元數(shù): | 64 |

| 輸入/輸出數(shù): | 80 |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-TQFP |

| 供應商設(shè)備封裝: | 100-TQFP(14x14) |

| 包裝: | 托盤 |

| 配用: | ATF15XX-DK3-ND - KIT DEV FOR ATF15XX CPLD'S |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁

18

3637B–PLD–1/08

ATF1504BE

Notes:

1. Peak-to-peak noise on VREF may not exceed ±2% VREF, VREF should track the variations in VCCIO.

2. VTT of transmitting device must track VREF of receiving devices.

9.

Timing Model

Table 8-7.

SSTL3-1 DC Voltage Specifications

Symbol

Parameter

Conditions

Min

Typ

Max

Units

VCCIO

Input Source Voltage

3.0

3.3

3.6

V

REF

Input Reference Voltage

1.3

1.5

1.7

V

TT

Termination Voltage

V

REF - 0.05

1.5

V

REF + 0.05

V

VIH

Input High Voltage

VREF + 0.4

VCCIO + 0.3

V

IL

Input Low Voltage

-0.3

V

REF - 0.6

V

VOH

Output High Voltage

IOH = -8 mA, VCCIO = 3V

VCCIO - 1.1

V

VOL

Output Low Voltage

IOL = 8 mA, VCCIO = 2.3V

0.7

V

IH(DC)

Input High Voltage

V

REF + 0.18

V

CCIO + 0.3

V

VIL(DC)

Input Low Voltage

-0.3

VREF - 0.18

V

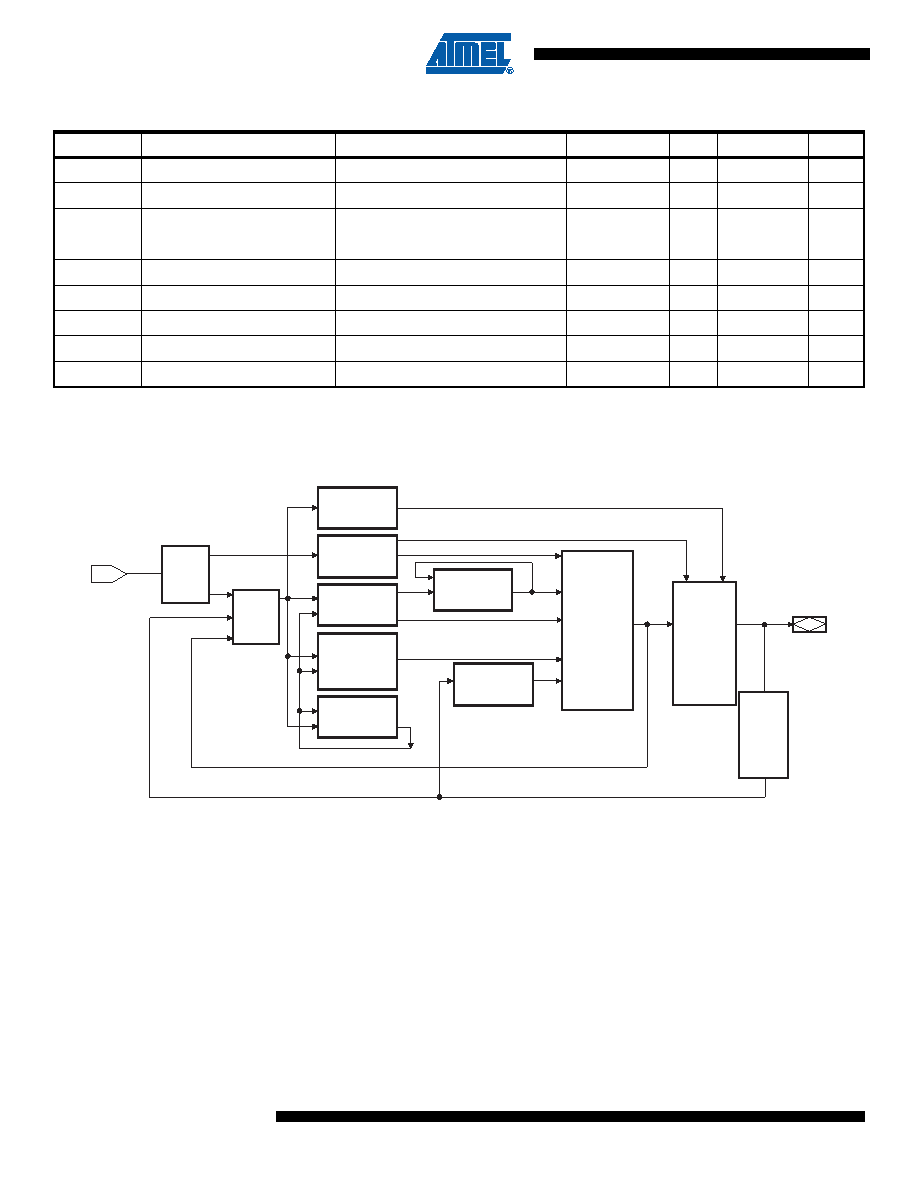

Input

Delay

t

IN

(+t

SCH)

Switch

Matrix

t

UIM

Internal Output

Enable Delay

t

IOE

Logic Array

Delay

t

LAD

Global Control

Delay

t

GLOB

Register

Control

Delay

t

LAC tIC tEN

Foldback Term

Delay

t

SEXP

Cascade Logic

Delay

t

PEXP

Fast Input

Delay

t

FIN

Register/

Combinatorial

Delays

t

SUI

t

HI

t

PRE

t

CLR

t

RD

t

COMB

t

FSUI

t

FHI

Output

Delay

t

OD1

(+t

SSO)

t

XZ

t

ZX1

t

ZX2

(+SSTL2-1_OAD)

(+SSTL3-1_OAD)

I/O

Delay

t

IO

(+t

SCH)

(+SSTL2-1_IAD)

(+SSTL3-1_IAD)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ATF1508ASL-25QI160 | IC CPLD 25NS LOW PWR 160PQFP |

| ATF1508ASVL-20JU84 | IC CPLD 20NS LOWV LOW PWR 84PLCC |

| ATF1508BE-5AX100 | IC CPLD 128MC 1.8V ISP 100TQFP |

| ATF1508RE-5AX100 | IC CPLD 128MC 3.3V ISP 100TQFP |

| ATF1508RE-7AU100 | IC CPLD EE 128MC 5NS 100-TQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ATF1504BE-5AX44 | 功能描述:CPLD - 復雜可編程邏輯器件 64 macrocell CPLD 1.8V RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ATF1504BE-7AU100 | 功能描述:CPLD - 復雜可編程邏輯器件 64MC CPLD 1.8V ISP RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ATF1504BE-7AU44 | 功能描述:CPLD - 復雜可編程邏輯器件 64 macrocell CPLD 1.8V RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ATF1504SE | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Family Datasheet |

| ATF1504SE(L) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATF1502/04/08/16SE(L) Preliminary [Updated 9/02. 69 Pages] Second Generation Industry Compatible 5V Logic Doubling CPLDs 32-512 Macrocells. standard & low power w/ISP |

發(fā)布緊急采購,3分鐘左右您將得到回復。