- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄295112 > ATF2500CL-20KC (ATMEL CORP) EE PLD, 20 ns, CQCC44 PDF資料下載

參數(shù)資料

| 型號(hào): | ATF2500CL-20KC |

| 廠商: | ATMEL CORP |

| 元件分類: | PLD |

| 英文描述: | EE PLD, 20 ns, CQCC44 |

| 封裝: | CERAMIC, LCC-44 |

| 文件頁數(shù): | 12/33頁 |

| 文件大?。?/td> | 698K |

| 代理商: | ATF2500CL-20KC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當(dāng)前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁

ATF2500C Family

2

The ATF2500C is organized around a single universal

array. All pins and feedback terms are always available to

every macrocell. Each of the 38 logic pins are array inputs,

as are the outputs of each flip-flop.

In the ATF2500C, four product terms are input to each sum

term. Furthermore, each macrocell’s three sum terms can

be combined to provide up to 12 product terms per sum

term with no performance penalty. Each flip-flop is individu-

ally selectable to be either D- or T-type, providing further

logic compaction. Also, 24 of the flip-flops may be

bypassed to provide internal combinatorial feedback to the

logic array.

Product terms provide individual clocks and asynchronous

resets for each flip-flop. The flip-flops may also be individu-

ally configured to have direct input pin clocking. Each

output has its own enable product term. Eight synchronous

preset product terms serve local groups of either four or

eight flip-flops. Register preload functions are provided to

simplify testing. All registers automatically reset upon

power-up.

The Atmel-unique “L” low-power feature is an edge-sensing

option that is now field programmable for the ATF2500C

family. The “L” feature utilizes Atmel-patented Input Transi-

tion Detection (ITD) circuitry and is activated by selecting

the “L” option from the program menu.

Using the ATF2500C Family’s Many

Advanced Features

The ATF2500Cs advanced flexibility packs more usable

ga tes in to 4 4 le ads th an ot he r PLDs. Som e of th e

ATF2500Cs key features are:

Fully Connected Logic Array – Each array input is

always available to every product term. This makes logic

placement a breeze.

Selectable D- and T-Type Registers – Each ATF2500C

flip-flop can be individually configured as either D- or T-

type. Using the T-type configuration, JK and SR flip-flops

are also easily created. These options allow more

efficient product term usage.

Buried Combinatorial Feedback – Each macrocell’s

Q2 register may be bypassed to feed its input (D/T2)

directly back to the logic array. This provides further logic

expansion capability without using precious pin

resources.

Selectable Synchronous/Asynchronous Clocking –

Each of the ATF2500Cs flip-flops has a dedicated clock

product term. This removes the constraint that all

registers use the same clock. Buried state machines,

counters and registers can all coexist in one device while

running on separate clocks. Individual flip-flop clock

source selection further allows mixing higher

performance pin clocking and flexible product term

clocking within one design.

A Total of 48 Registers – The ATF2500C provides two

flip-flops per macrocell – a total of 48. Each register has

its own clock and reset terms, as well as its own sum

term.

Independent I/O Pin and Feedback Paths – Each I/O

pin on the ATF2500C has a dedicated input path. Each

of the 48 registers has its own feedback term into the

array as well. These features, combined with individual

product terms for each I/O’s output enable, facilitate true

bi-directional I/O design.

Combinable Sum Terms – Each output macrocell’s

three sum terms may be combined into a single term.

This provides a fan in of up to 12 product terms per sum

term with no speed penalty.

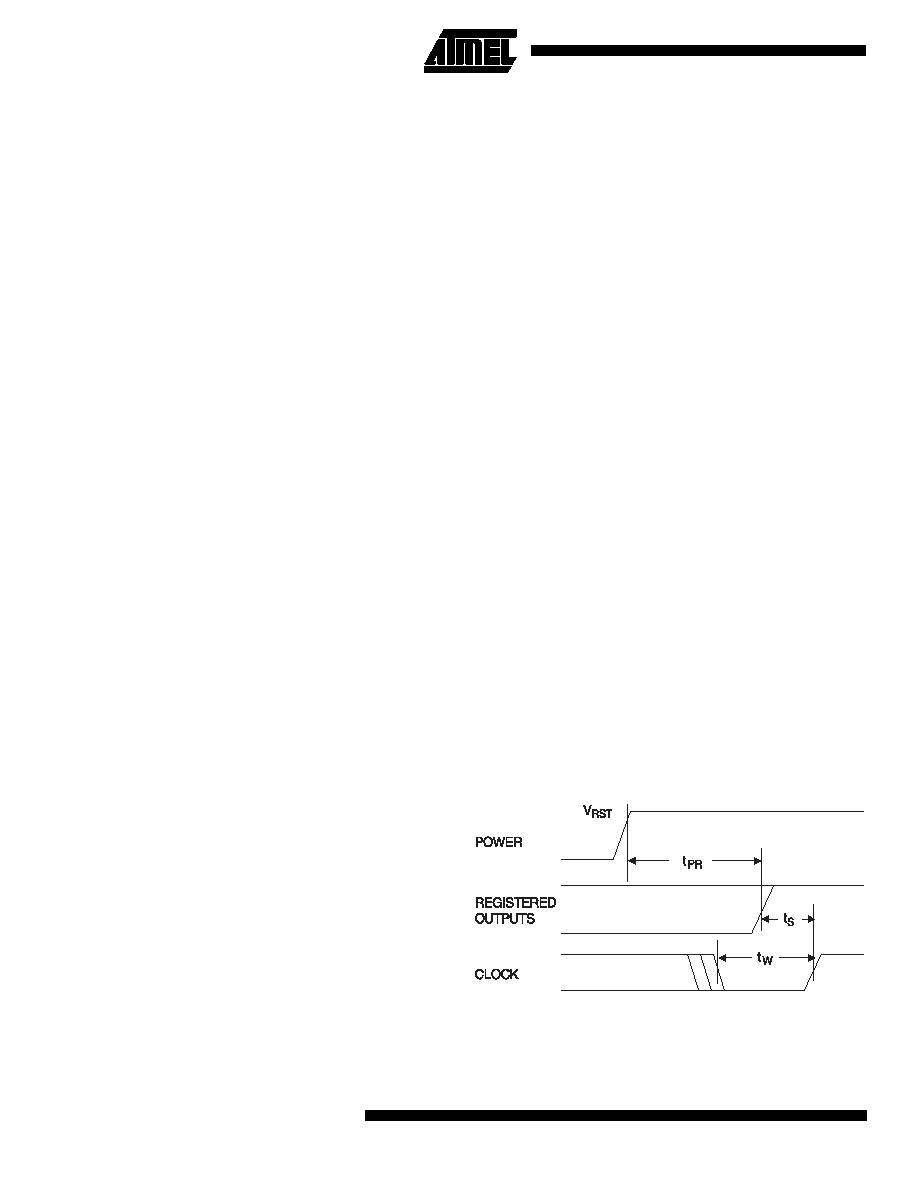

Power-up Reset

The registers in the ATF2500Cs are designed to reset dur-

ing power-up. At a point delayed slightly from V

CC crossing

V

RST, all registers will be reset to the low state. The output

state will depend on the polarity of the output buffer.

This feature is critical for state as nature of reset and the

uncertainty of how V

CC actually rises in the system, the fol-

lowing conditions are required:

1.

The V

CC rise must be monotonic,

2.

After reset occurs, all input and feedback setup

times must be met before driving the clock pin or

terms high, and

3.

The clock pin, and any signals from which clock

terms are derived, must remain stable during t

PR.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ATF2500CL-20KM | EE PLD, 20 ns, CQCC44 |

| ATF2500CL-20NM | EE PLD, 20 ns, CQCC44 |

| ATF2500CQ-25GM/883 | EE PLD, 25 ns, CDIP40 |

| ATF2500CQ-25JC | EE PLD, 25 ns, PQCC44 |

| ATF2500CQ-25JI | EE PLD, 25 ns, PQCC44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ATF25100 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRANSISTOR | JFET | N-CHANNEL | 50MA I(DSS) | CHIP |

| ATF25170 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRANSISTOR | JFET | N-CHANNEL | 50MA I(DSS) | MICRO-XVAR |

| ATF-25170 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:0.5-10 GHz Low Noise Gallium Arsenide FET |

| ATF25570 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRANSISTOR | JFET | N-CHANNEL | 50MA I(DSS) | MICRO-XVAR |

| ATF-25570 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:0.5-10 GHz General Purpose Gallium Arsenide FET |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。