- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄295115 > AX1000-1FG676I FPGA, 12096 CLBS, 612000 GATES, 763 MHz, PBGA676 PDF資料下載

參數(shù)資料

| 型號(hào): | AX1000-1FG676I |

| 元件分類(lèi): | FPGA |

| 英文描述: | FPGA, 12096 CLBS, 612000 GATES, 763 MHz, PBGA676 |

| 封裝: | 1 MM PITCH, FBGA-676 |

| 文件頁(yè)數(shù): | 204/230頁(yè) |

| 文件大小: | 6485K |

| 代理商: | AX1000-1FG676I |

Axcelerator Family FPGAs

v2.8

2-61

The HM and CM modules can select between:

The HCLK or CLK source respectively

A local signal routed on generic routing resources

This

allows

each

core

tile

to

have

eight

clocks

independent of the other core tiles in the device.

Both HCLK and CLK are segmentable, meaning that

individual branches of the global resource can be used

independently.

Like the HM and CM modules, the HD and RD modules

can select between:

The HCLK or CLK source from the HM or CM

module respectively

A local signal routed on generic routing resources

The AX architecture is capable of supporting a large

number of local clocks – 24 segments per HCLK driving

north-south and 28 segments per CLK driving east-west

per core tile.

Actel's

Designer

software’s

place-and-route

takes

advantage of the segmented clock structure found in

Axcelerator devices by turning off any unused clock

segments. This results in not only better performance but

also lower power consumption.

Global Resource Access Macros

Global resources can be driven by one of three sources:

external pad(s), an internal net, or the output of a PLL.

These connections can be made by using one of three

types of macros: CLKBUF, CLKINT, and PLLCLK.

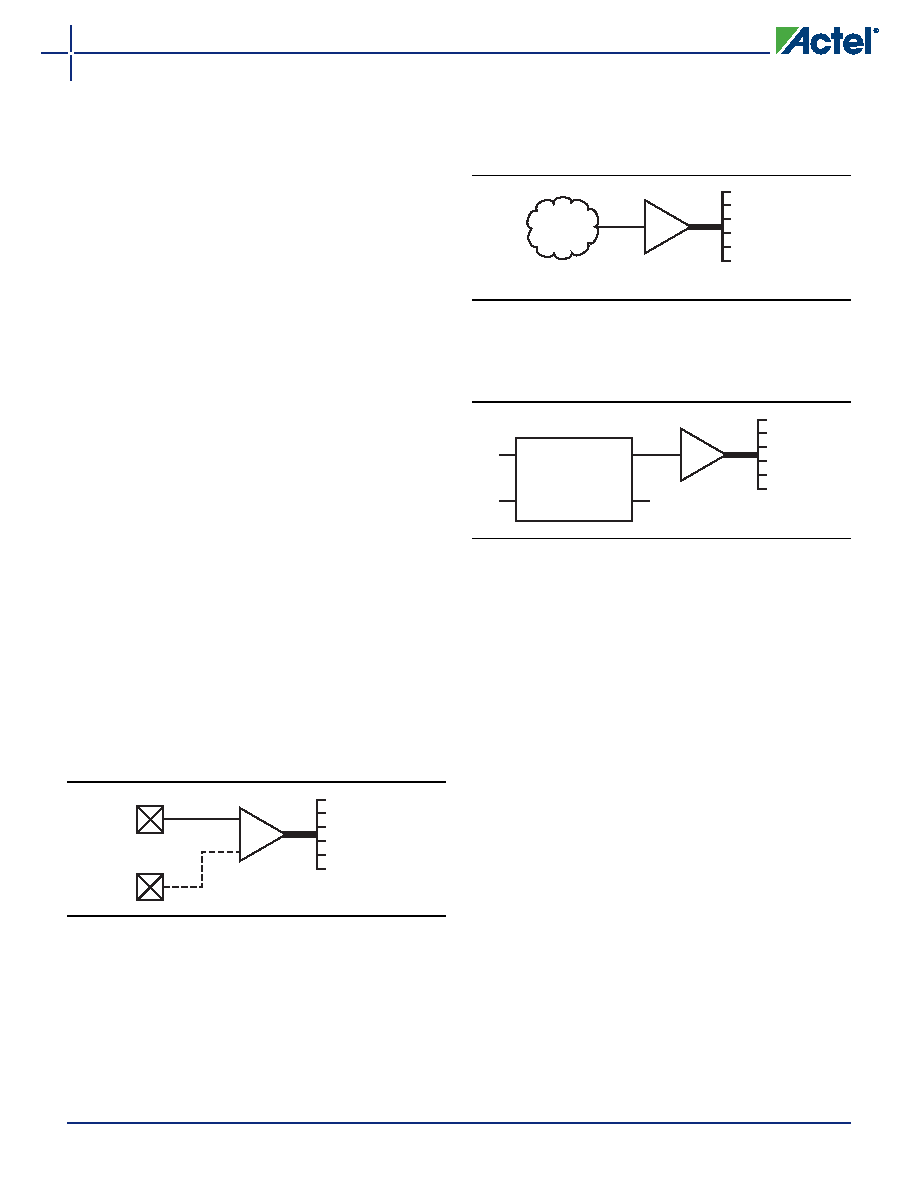

CLKBUF and HCLKBUF

CLKBUF (HCLKBUF) is used to drive a CLK (HCLK) from

external pads. These macros can be used either

generically or with the specific I/O standard desired

(e.g.

CLKBUF_LVCMOS25,

HCLKBUF_LVDS,

etc.)

(Figure 2-42).

Package pins CLKEP and CLKEN are associated with

CLKE; package pins HCLKAP and HCLKAN are

associated with HCLKA, etc.

Note that when CLKBUF (HCLKBUF) is used with a

single-ended I/O standard, it must be tied to the P-

pad of the CLK (HCLK) package pin. In this case, the

CLK (HCLK) N-pad can be used for user signals.

CLKINT and HCLKINT

CLKINT (HCLKINT) is used to access the CLK (HCLK)

resource internally from the user signals (Figure 2-43).

PLLRCLK and PLLHCLK

PLLRCLK (PLLHCLK) is used to drive global resource

CLK (HCLK) from a PLL (Figure 2-44).

Using Global Resources with PLLs

Each global resource has an associated PLL at its root. For

example, PLLA can drive HCLKA, PLLE can drive CLKE, etc.

In addition, each clock pin of the package can be used to

drive either its associated global resource or PLL. For

example, package pins CLKEP and CLKEN can drive either

the RefCLK input of PLLE or CLKE.

There are two macros required when interfacing the

embedded PLLs with the global resources: PLLINT and PLLOUT.

PLLINT

This macro is used to drive the RefCLK input of the PLL

internally from user signals.

PLLOUT

This macro is used to connect either the CLK1 or CLK2

output of a PLL to the regular routing network (Figure 2-

Figure 2-42 CLKBUF and HCLKBUF

P

N

CLKBUF

HCLKBUF

Clock

Network

Figure 2-43 CLKINT and HCLKINT

Figure 2-44 PLLRCLK and PLLHCLK

CLKINT

HCLKINT

Clock

Network

Logic

PLLRCLK

PLLHCLK

Clock

Network

CLK1

CLK2

FB

RefCLK

PLL

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AX1000-1FG676MX79 | FPGA, 12096 CLBS, 612000 GATES, 763 MHz, PBGA676 |

| AX1000-1FG676M | FPGA, 12096 CLBS, 612000 GATES, 763 MHz, PBGA676 |

| AX1000-1FG676X79 | FPGA, 12096 CLBS, 612000 GATES, 763 MHz, PBGA676 |

| AX1000-1FG676 | FPGA, 12096 CLBS, 612000 GATES, 763 MHz, PBGA676 |

| AX1000-1FG896IX79 | FPGA, 12096 CLBS, 612000 GATES, 763 MHz, PBGA896 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AX1000-1FG676M | 制造商:Microsemi Corporation 功能描述:FPGA Axcelerator Family 612K Gates 12096 Cells 763MHz 0.15um Technology 1.5V 676-Pin FBGA 制造商:Microsemi Corporation 功能描述:FPGA AXCELERATOR 612K GATES 12096 CELLS 763MHZ 0.15UM 1.5V 6 - Trays |

| AX1000-1FG896 | 功能描述:IC FPGA AXCELERATOR 1M 896-FBGA RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:Axcelerator 產(chǎn)品培訓(xùn)模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標(biāo)準(zhǔn)包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計(jì):6635520 輸入/輸出數(shù):270 門(mén)數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類(lèi)型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FBGA(23x23) |

| AX1000-1FG896B | 制造商:ACTEL 制造商全稱(chēng):Actel Corporation 功能描述:Axcelerator Family FPGAs |

| AX1000-1FG896I | 功能描述:IC FPGA AXCELERATOR 1M 896-FBGA RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:Axcelerator 產(chǎn)品培訓(xùn)模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標(biāo)準(zhǔn)包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計(jì):6635520 輸入/輸出數(shù):270 門(mén)數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類(lèi)型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FBGA(23x23) |

| AX1000-1FG896M | 制造商:Microsemi Corporation 功能描述:FPGA Axcelerator Family 612K Gates 12096 Cells 763MHz 0.15um Technology 1.5V 896-Pin FBGA 制造商:Microsemi Corporation 功能描述:FPGA AXCELERATOR 612K GATES 12096 CELLS 763MHZ 0.15UM 1.5V 8 - Trays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。