- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄223461 > BU-61703G4-172K (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, MQFP72 PDF資料下載

參數(shù)資料

| 型號(hào): | BU-61703G4-172K |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, MQFP72 |

| 封裝: | 1 X 1 INCH, GULL WING, PACKAGE-72 |

| 文件頁數(shù): | 16/52頁 |

| 文件大?。?/td> | 367K |

| 代理商: | BU-61703G4-172K |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

23

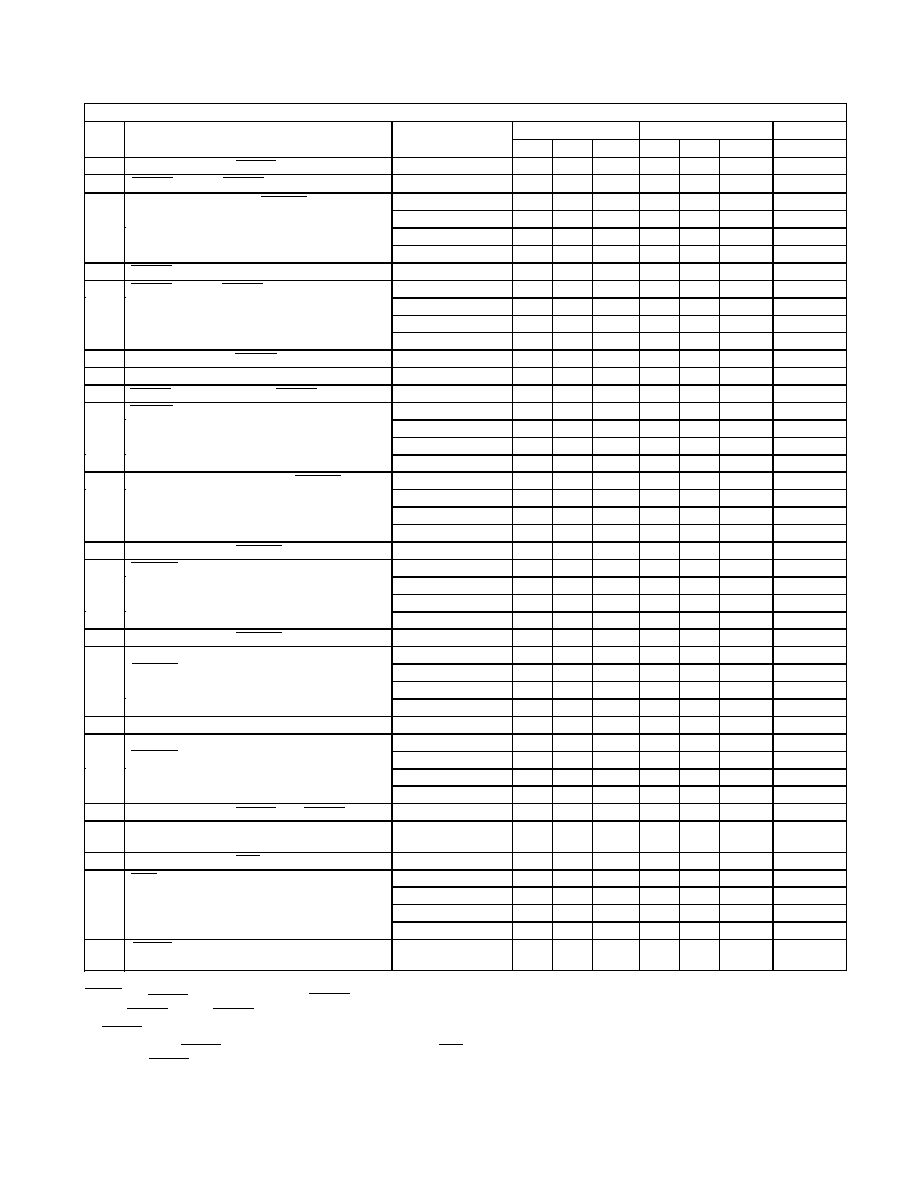

TABLE FOR FIGURE 9. SSRT DMA WRITE (BURST MODE) TIMING

VALUE @ 5 Volts

VALUE @ 3.3 Volts

UNITS

REF

DESCRIPTION

CLOCK

FREQUENCY

MIN

TYP

MAX

MIN

TYP

MAX

t1

CLOCK IN rising to DTREQ low

ALL

40

ns

t2

DTREQ falling to DTGRT low

ALL

10

s

20 MHz

60

ns

16 MHz

85

ns

12 MHz

127

ns

t3

CWC setup time prior to MEMWR falling for first

word of burst transfer (see Note 1)

10 MHz

160

ns

t4

DTGRT low setup prior to CLOCK IN rising edge

ALL

10

15

ns

20 MHz

100

105

ns

16 MHz

113

118

ns

12 MHz

133

138

ns

t5

DTGRT falling to DTACK low

10 MHz

150

155

ns

t6

CLOCK IN rising to DTACK low

ALL

40

ns

t7

Data output valid following CLOCK IN

ALL

40

ns

t8

DTGRT hold time following DTACK falling

ALL

30

ns

20 MHz

290

300

290

300

ns

16 MHz

365

375

365

375

ns

12 MHz

490

500

490

500

ns

t9

DTACK low pulse width (based on a two data

word transfer)

(see Note 2)

10 MHz

590

600

590

600

ns

20 MHz

10

ns

16 MHz

22

ns

12 MHz

43

ns

t10

Data output setup time prior to MEMWR low

10 MHz

60

ns

t11

CLOCK IN rising to MEMWR low

ALL

40

ns

20 MHz

40

50

40

50

ns

16 MHz

52.5

62.5

52.5

62.5

ns

12 MHz

73.3

83.3

73.3

83.3

ns

t12

MEMWR low pulse width

10 MHz

90

100

90

100

ns

t13

CLOCK IN rising to MEMWR high

ALL

30

40

ns

20 MHz

20

10

ns

16 MHz

33

23

ns

12 MHz

53

43

ns

t14

Data output and CWC hold time following

MEMWR high

10 MHz

70

60

ns

t15

Data output hold time following CLOCK IN rising

ALL

10

15

ns

20 MHz

10

ns

16 MHz

23

ns

12 MHz

43

ns

t16

CWC (all but first data word) setup time prior to

MEMWR low

10 MHz

60

ns

t17

CLOCK IN rising to DTREQ and DTACK high

ALL

30

40

ns

t18

Data output signal Tri-State following CLOCK IN

rising

ALL

40

ns

t19

CLOCK IN rising to GBR falling edge

ALL

40

ns

20 MHz

90

100

90

100

ns

16 MHz

115

125

115

125

ns

12 MHz

157

167

157

167

ns

t20

GBR low pulse width

10 MHz

190

200

190

200

ns

t21

INCMD rising following CLOCK IN rising

(see Note 3)

ALL

30

40

ns

Notes:

1. Assume DTGRT is low at the time that DTREQ is asserted low. If not, then this time will increase by the amount of

the DTREQ(low)-to-DTGRT(low) delay.

2. DTACK pulse width is 3 clock cycles per data word transfer

3. Rising edge of INCMD will immediately follow the rising edge of GBR only for a broadcast message. For a non-broadcast message, the rising

edge of INCMD will occur after the mid-parity crossing of the RT status response. This additional delay time is approximately 96 clock

cycles: 9.6 s at 10 MHz, 8 s at 12 MHz, 6.0 s at 16 MHz, or 4.8 s at 20 MHz.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BU-61703G4-172Q | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, MQFP72 |

| BU-61703G4-172S | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, MQFP72 |

| BU-61703G4-172W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, MQFP72 |

| BU-61703G4-182Z | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, MQFP72 |

| BU-61703G4-192Y | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, MQFP72 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BU-61705 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |Simple System RT |

| BU-61740B3NEW | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |μ-ACE (Micro-ACE?) |

| BU-61743 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |Enhanced Mini-ACE? |

| BU-61743F3-100 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| BU-61743F3-110 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。