- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16573 > BUF20820EVM (Texas Instruments)EVAL MOUDLE FOR BUF20820 PDF資料下載

參數(shù)資料

| 型號(hào): | BUF20820EVM |

| 廠商: | Texas Instruments |

| 文件頁數(shù): | 29/29頁 |

| 文件大小: | 0K |

| 描述: | EVAL MOUDLE FOR BUF20820 |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁

BUF20820

SBOS330E DECEMBER 2005 REVISED OCTOBER 2008

www.ti.com

9

ACQUIRE OF OTP MEMORY

A general acquire command will update all registers and

DAC outputs to the values stored in OTP memory.

A single channel acquire command will update only the

register and DAC output of the DAC corresponding to the

DAC address used in the command.

General Acquire Command

1.

Send a START condition on the bus.

2.

Send the device address and read/write bit = LOW.

The BUF20820 will acknowledge this byte.

3.

Send a DAC address byte. Bits D7D5 must be set

to 100. Bits D4D0 are any valid DAC address.

Only addresses 00000 to 10100 are valid and will

be

acknowledged.

Table 3 shows the valid

addresses.

4.

Send a STOP condition on the bus.

Following this command, all DAC registers and DAC

outputs will change to the OTP memory values.

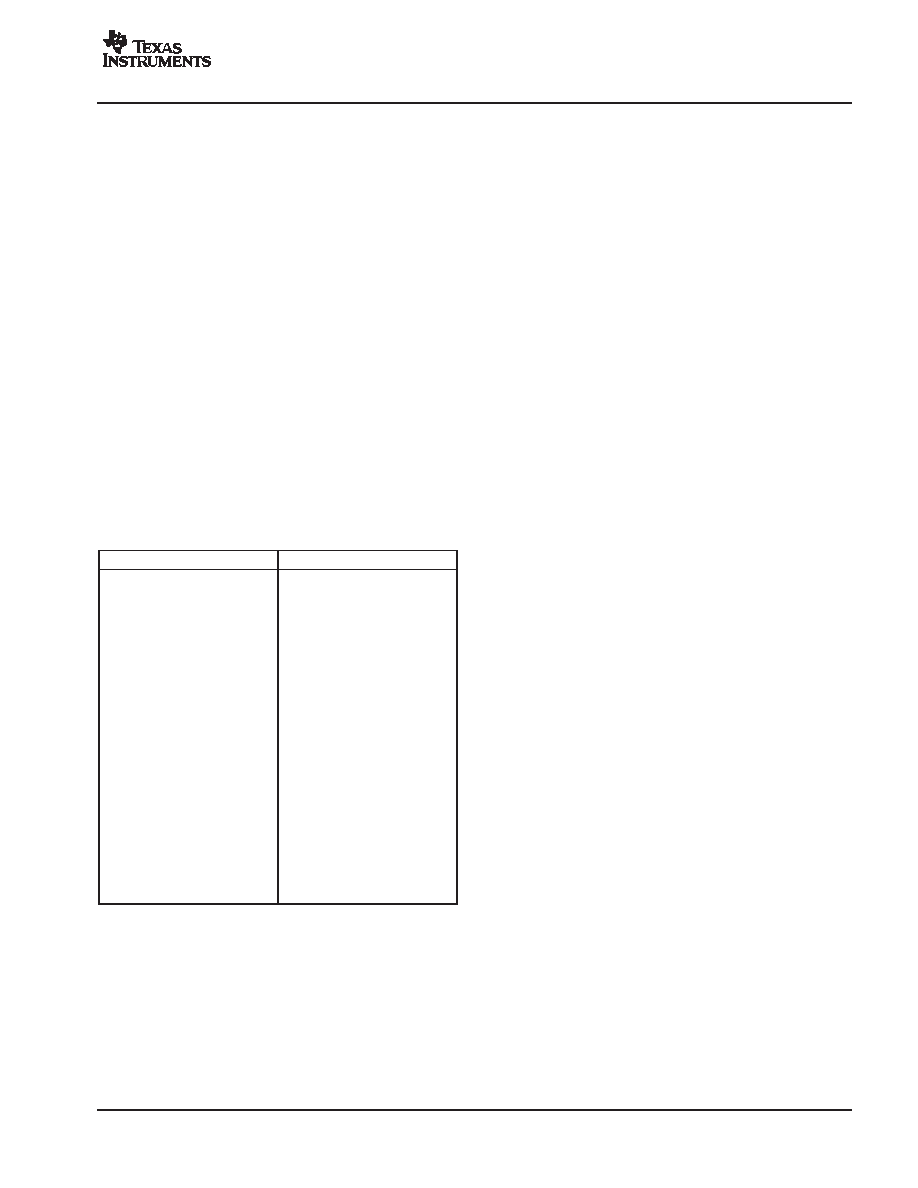

Table 3. DAC Addresses

DAC

ADDRESS

DAC_1

0 0000

DAC_2

0 0001

DAC_3

0 0010

DAC_4

0 0011

DAC_5

0 0100

DAC_6

0 0101

DAC_7

0 0110

DAC_8

0 0111

DAC_9

0 1000

DAC_10

0 1001

DAC_11

0 1010

DAC_12

0 1011

DAC_13

0 1100

DAC_14

0 1101

DAC_15

0 1110

DAC_16

0 1111

DAC_17

1 0000

DAC_18

1 0001

VCOM OUT1

1 0010

VCOM OUT2

1 0011

Write Disable Bit

1 0100

Single Channel Acquire Command

1.

Send a START condition on the bus.

2.

Send the device address and read/write bit = LOW.

The BUF20820 will acknowledge this byte.

3.

Send a DAC address byte using the DAC address

corresponding to the DAC output and register to

update with the OTP memory value. Bits D7D5 must

be set to 010. Bits D4D0 are the DAC address. Only

DAC addresses 00000 to 10100 are valid and will be

acknowledged. Table 3 shows the valid addresses.

4.

Send a STOP condition on the bus.

See Figure 9 for the timing diagrams for the acquire

commands.

READ/WRITE OPERATIONS

Single or multiple read and write operations can be done

in a single communication transaction. Writing to a DAC

register differs from writing to the OTP memory.

Bits

D15D14 of the most significant byte of data will determine

if data will be written to the DAC register or the OTP

memory. See Figure 10 through Figure 12 for the timing

diagrams and timing requirements for the read/write

commands.

Read/Write: DAC register

The BUF20820 is able to read from a single DAC, or

multiple DACs, or write to the register of a single DAC, or

multiple DACs in a single communication transaction.

DAC addresses begin with 00000, which corresponds to

DAC_1, through 10011, which corresponds to VCOM OUT2.

Write commands are performed by setting the read/write

bit LOW. Setting the read/write bit HIGH will perform a read

transaction.

Writing:

To write to a single DAC register:

1.

Send a START condition on the bus.

2.

Send the device address and read/write bit = LOW.

The BUF20820 will acknowledge this byte.

3.

Send a DAC or write disable bit address byte. Bits

D7D5 must be set to 0. Bits D4D0 are the DAC

address. Only addresses 00000 to 10100 are valid

and will be acknowledged. Table 3 shows valid

addresses.

4.

Send two bytes of data for the specified DAC register.

Begin by sending the most significant byte first (bits

D15D8, of which only bits D9 and D8 are used, and

bits D15D14 must not be 01), followed by the least

significant byte (bits D7D0). For address 10100, only

D0 has meaning. This bit is the write disable bit. The

register is updated after receiving the second byte.

5.

Send a STOP condition on the bus.

The BUF20820 will acknowledge each data byte. If the

master terminates communication early by sending a

STOP or START condition on the bus, the specified

register will not be updated. Updating the DAC register is

not the same as updating the DAC output voltage. See the

Output Latch section.

The process of updating multiple DAC registers begins the

same as when updating a single register. However,

instead of sending a STOP condition after writing the

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M1BXA-2436R | IDC CABLE - MSR24A/MC24M/X |

| RBM06DCMT | CONN EDGECARD 12POS .156 WW |

| GBC10DRSN-S273 | CONN EDGECARD 20POS DIP .100 SLD |

| GEM25DTMT-S189 | CONN EDGECARD 50POS R/A .156 SLD |

| SRP7030-R47M | INDUCTOR SHIELDED PWR 0.47UH SMD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BUF22821 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Programmable Gamma-Voltage Generator and VCOM Calibrator with Integrated Two-Bank Memory |

| BUF22821AIDCPR | 功能描述:LCD Gamma緩沖器 Prgrmbl Gam-Vltg Gen & Vcom Calibrator RoHS:否 制造商:Maxim Integrated 輸入補(bǔ)償電壓: 轉(zhuǎn)換速度: 電源電壓-最大:20 V 電源電壓-最小:9 V 電源電流: 最大功率耗散: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TQFN-38 封裝:Tube |

| BUF22821EVM | 功能描述:放大器 IC 開發(fā)工具 BUF22821EVM Eval Mod RoHS:否 制造商:International Rectifier 產(chǎn)品:Demonstration Boards 類型:Power Amplifiers 工具用于評(píng)估:IR4302 工作電源電壓:13 V to 23 V |

| BUF22821EVM-USB | 功能描述:放大器 IC 開發(fā)工具 BUF22821 Eval board Mod RoHS:否 制造商:International Rectifier 產(chǎn)品:Demonstration Boards 類型:Power Amplifiers 工具用于評(píng)估:IR4302 工作電源電壓:13 V to 23 V |

| BUF298AF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRANSISTOR | BJT POWER MODULE | INDEPENDENT | 450V V(BR)CEO | 50A I(C) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。