- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄26509 > CS495314-CVZ (CIRRUS LOGIC INC) PDF資料下載

參數(shù)資料

| 型號: | CS495314-CVZ |

| 廠商: | CIRRUS LOGIC INC |

| 元件分類: | 顏色信號轉換 |

| 中文描述: | COLOR SIGNAL DECODER, PQFP128 |

| 封裝: | LEAD FREE, LQFP-128 |

| 文件頁數(shù): | 28/35頁 |

| 文件大小: | 295K |

| 代理商: | CS495314-CVZ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

CS4953xx Data Sheet

32-bit Audio Decoder DSP Family

DS705PP8

34

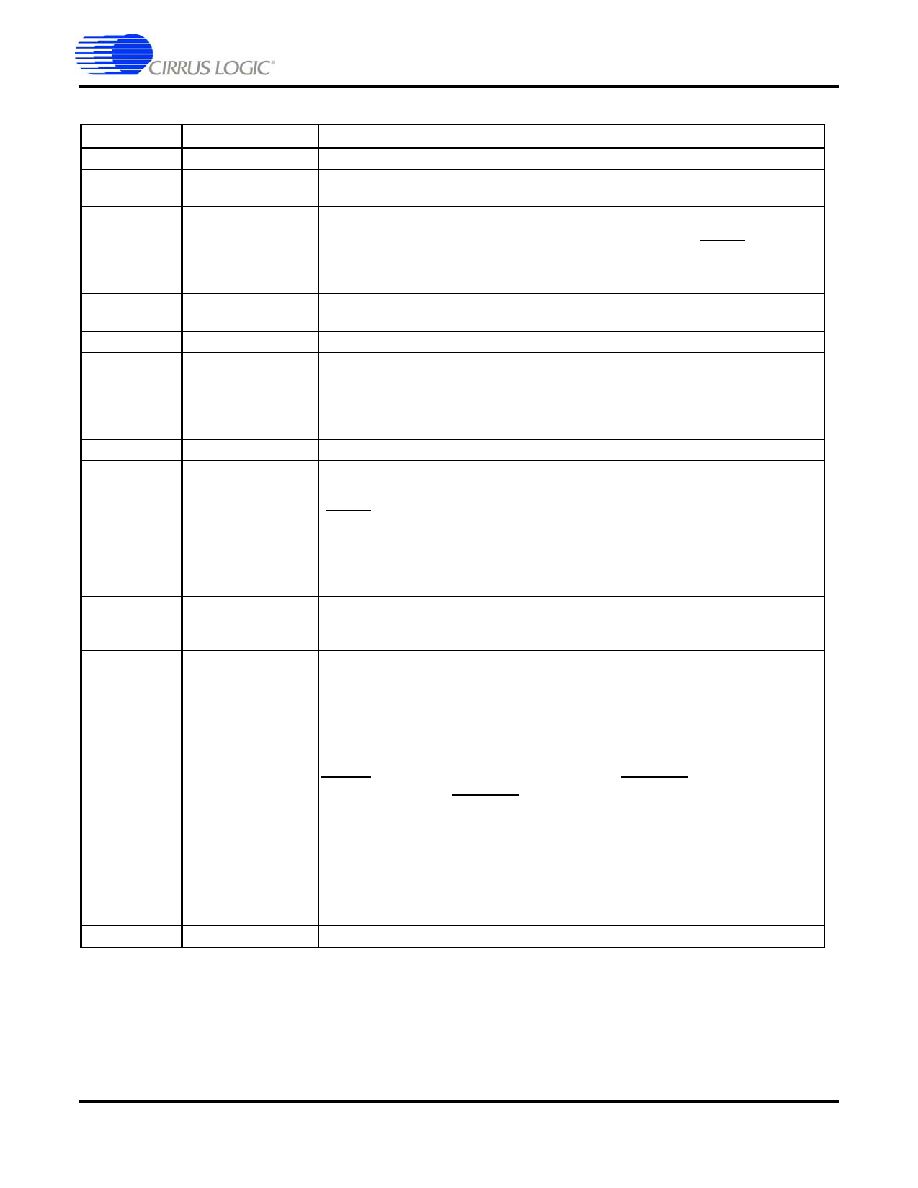

10 Revision History

Revision

Date

Changes

A1

FEB 2006

Advance release.

A2

JUN 2006

Updated part numbers for ordering (Tables 5 & 6), Updated VOH and VOL

specification to include the current load used for testing

A3

JUL 2006

Updated part numbers for ordering (Tables 5 & 6). Updated text in sections 3 and 4.

Updated parameter descriptions in sections 5.1 and 5.3. Updated Tspickl, Tspickh,

and Tspidov timing. Corrected Figure SPI Master Timing to use EE_CS. Added foot-

note to XTI table. Removed SCLK/LRCLK relative timing from DAI port timing.

Removed SCLK/LRCLK slave relative timing from DAO port timing.

A4

OCT 2007

Updated the Tspidsu, Tspickl, and Tspickh timing parameters for master mode SPI.

This applies to both SPI ports.

PP1

May 28, 2008

PP2

June 20, 2008

Added typical crystal frequency values in Table Footnote 1 and minimum and

SCP_CLK in Section 5.11. Redefined DC leakage characterization data in

, correcting units of measurement. Modified Footnote 1 under

PP3

September 24, 2008

Removed references to External Parallel Flash / SRAM Interface.

PP4

June 9, 2009

Updated product number references in Section 5.9, Section 6

2,

designation from “#” character after the pin name to a line over the pin name as in

“EE_CS”. Removed Active Low designation from the BDI_REQ pin in the 128-pin

pinout drawings in Figure 19 and Figure 20, and in the 144-pin pinout drawings in

PP5

July 29, 2009

family be used with new designs. Updated Section 2

PP6

November 11, 2009

Removed references to UART port. Removed references to 11.2896,

18.432, and 27 MHz frequency clocks in Note 1 in Section 5.8 “Switching

Characteristics — XTI” on page 12 and the minimum and maximum

External Crystal Operating Frequency values in that same section. Updated

page 31, moved SCP2_SDA from Pin 106 to Pin 105, deleted duplicate

EE_CS from Pin 25, and designated Pin 140 BDI_REQ as active low.

Designated Pin 32, BDI_REQ as active low In Figure 19, "128-pin LQFP

Section 5.3, the parameter, “Input leakage current (all digital pins with

internal pull-up resistors enabled, and XTI)”, Max value changes from 50

μA

to 70

μA. In Section 5.13, the parameter SCP_CLK low to SCP_SDA out

valid with symbol “tiicdov” maximum value changes from 18 ns to 36 ns.

PP7

June 2, 2010

Updated Table 5 to show status of various parts.

相關PDF資料 |

PDF描述 |

|---|---|

| CS495314-CVZR | |

| CS495314-DVZ | |

| CS495314-DVZR | |

| CS495304-CVZ | |

| CS495304-CVZR | |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| CS495314-CVZR | 功能描述:音頻 DSP IC 32bit Decoder DSP w/Dual DSP Engine RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風格: 封裝 / 箱體: 封裝:Tube |

| CS495314-DVZ | 功能描述:音頻 DSP IC Multi-Channel Audio DSP Decoder RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風格: 封裝 / 箱體: 封裝:Tube |

| CS495314-DVZR | 功能描述:音頻 DSP IC Multi-Channel Audio DSP Decoder RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風格: 封裝 / 箱體: 封裝:Tube |

| CS4953-CL | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:NTSC/PAL Digital Video Encoder |

| CS4953-CQ | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:NTSC/PAL Digital Video Encoder |

發(fā)布緊急采購,3分鐘左右您將得到回復。