- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄295335 > CS5165GDWR16 (ON SEMICONDUCTOR) 1.5 A SWITCHING CONTROLLER, 1000 kHz SWITCHING FREQ-MAX, PDSO16 PDF資料下載

參數(shù)資料

| 型號(hào): | CS5165GDWR16 |

| 廠商: | ON SEMICONDUCTOR |

| 元件分類: | 穩(wěn)壓器 |

| 英文描述: | 1.5 A SWITCHING CONTROLLER, 1000 kHz SWITCHING FREQ-MAX, PDSO16 |

| 封裝: | SOIC-16 |

| 文件頁(yè)數(shù): | 8/21頁(yè) |

| 文件大小: | 718K |

| 代理商: | CS5165GDWR16 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)

CS5165

http://onsemi.com

16

It is therefore required that the output voltage attains an

out of regulation or in regulation level for at least the builtin

delay time duration before the Power Good signal can

change state.

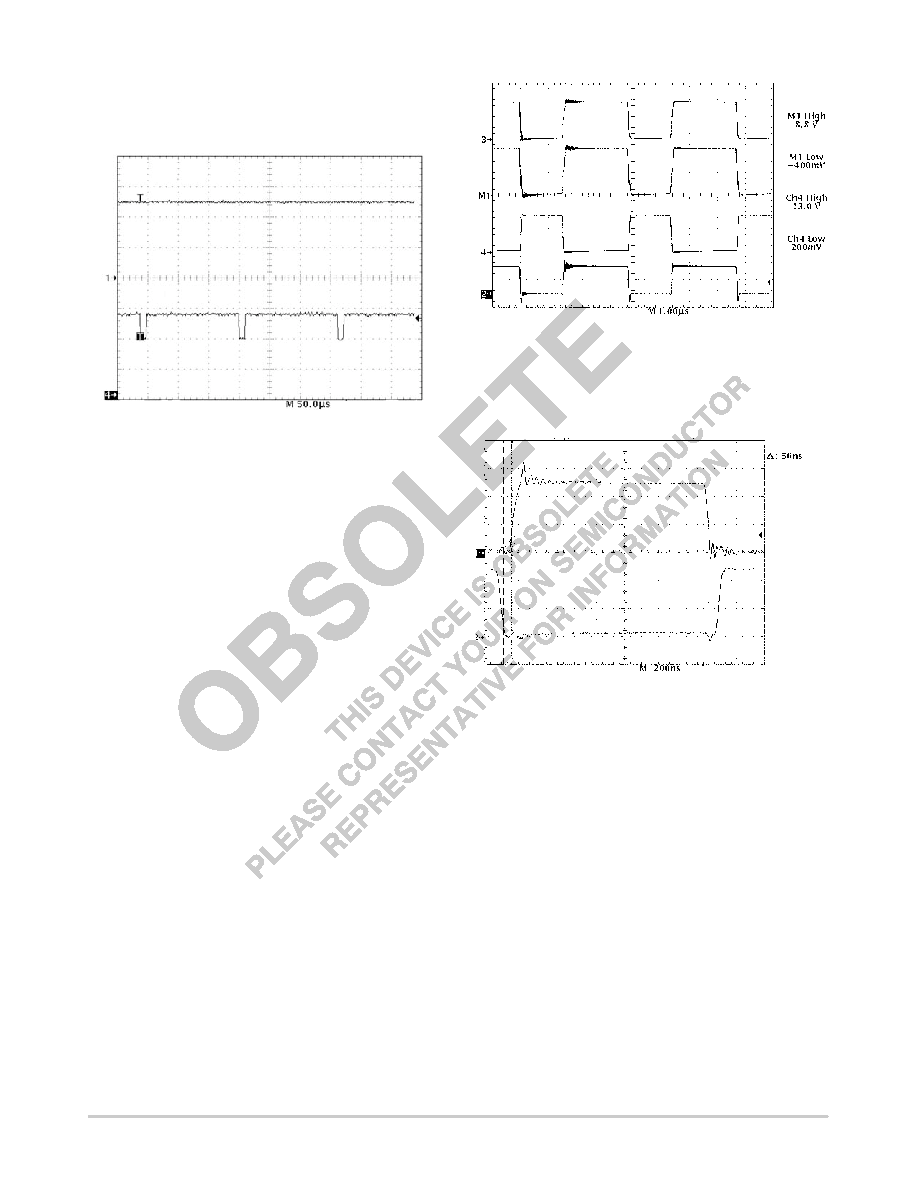

Figure 25. Power Good is Insensitive to Out of

Regulation Conditions that are Present for a

Duration Less Than the Built In Delay

Trace 4 VFB (1.0 V/div.)

Trace 2 PWRGD (2.0 V/div.)

Selecting External Components

The CS5165 buck regulator can be used with a wide range

of external power components to optimize the cost and

performance of a particular design. The following

information can be used as general guidelines to assist in

their selection.

NFET Power Transistors

Both logic level and standard FETs can be used. The

reference designs derive gate drive from the 12 V supply

which is generally available in most computer systems and

utilize logic level FETs. A charge pump may be easily

implemented to support 5.0 V only systems. Multiple FET’s

may be paralleled to reduce losses and improve efficiency

and thermal management.

Voltage applied to the FET gates depends on the

application circuit used. Both upper and lower gate driver

outputs are specified to drive to within 1.5 V of ground when

in the low state and to within 2.0 V of their respective bias

supplies when in the high state. In practice, the FET gates

will be driven rail to rail due to overshoot caused by the

capacitive load they present to the controller IC. For the

typical application where VCC = 12 V and 5.0 V is used as

the source for the regulator output current, the following

gate drive is provided:

VGS(BOTTOM) + 12 V

VGS(TOP) + 12 V * 5.0 V + 7.0 V

(see Figure 26)

Figure 26. Gate Drive Waveforms Depicting

Rail to Rail Swing

Trace 3 GATE(H) (10 V/div.)

Trace 1 GATE(H) 5.0 VIN

Trace 4 GATE(L) (10 V/div.)

Trace 2 Inductor Switching Node (5.0 V/div.)

Figure 27. Normal Operation Showing the Guaranteed

NonOverlap Time Between the High and LowSide

MOSFET Gate Drives, ILOAD = 14 A

Trace 1 = GATE(H) (5.0 V/div.)

Trace 2 = GATE(L) (5.0 V/div.)

@ 2.2 V

The CS5165 provides adaptive control of the external

NFET conduction times by guaranteeing a typical 65 ns

nonoverlap between the upper and lower MOSFET gate

drive pulses. This feature eliminates the potentially

catastrophic effect of “shootthrough current”, a condition

during which both FETs conduct causing them to overheat,

selfdestruct, and possibly inflict irreversible damage to the

processor.

The most important aspect of FET performance is

RDSON, which effects regulator efficiency and FET thermal

management requirements.

The power dissipated by the MOSFETs may be estimated

as follows:

Switching MOSFET:

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CS5332GDW28 | 1.5 A SWITCHING CONTROLLER, 1000 kHz SWITCHING FREQ-MAX, PDSO28 |

| CS600/L2 | 1 CHANNEL LOGIC OUTPUT OPTOCOUPLER |

| CSBLA384KECE-B0 | CERAMIC RESONATOR, 0.384 MHz |

| CSC5026-0102F | 16 CONTACT(S), COMBINATION LINE CONNECTOR, SOCKET |

| CSD10030 | ZERO RECOVERY RECTIFIER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CS-5165HDW16 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Voltage-Mode SMPS Controller |

| CS-5165HDWR16 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Voltage-Mode SMPS Controller |

| CS5165HGDW16 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS5165HGDWR16 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS5166 | 功能描述:SCREWDRIVER,5/16"X6",SLOTTED 制造商:apex tool group 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。