- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1909 > CS82C59A-1296 (Intersil)IC CTRL INTERRUPT 12.5MHZ 28PLCC PDF資料下載

參數(shù)資料

| 型號: | CS82C59A-1296 |

| 廠商: | Intersil |

| 文件頁數(shù): | 22/22頁 |

| 文件大小: | 0K |

| 描述: | IC CTRL INTERRUPT 12.5MHZ 28PLCC |

| 標(biāo)準(zhǔn)包裝: | 750 |

| 控制器類型: | CMOS 優(yōu)先中斷控制器 |

| 接口: | 系統(tǒng)總線 |

| 電源電壓: | 4.5 V ~ 5.5 V |

| 電流 - 電源: | 1mA |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 28-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 28-PLCC(11.51x11.51) |

| 包裝: | 帶卷 (TR) |

9

FN2784.5

March 17, 2006

e. If lC4 = 0, then all functions selected in lCW4 are set to

zero. (Non-Buffered mode (see note), no Auto-EOI,

8080/85 system).

NOTE: Master/Slave in ICW4 is only used in the buffered mode.

Initialization Command Words 1 and 2 (ICW1, lCW2)

A5 - A15: Page starting address of service routines. In an

8080/85 system the 8 request levels will generate CALLS to

8 locations equally spaced in memory. These can be

programmed to be spaced at intervals of 4 or 8 memory

locations, thus, the 8 routines will occupy a page of 32 or 64

bytes, respectively.

The address format is 2 bytes long (A0 - A15). When the

routine interval is 4, A0 - A4 are automatically inserted by the

82C59A, while A5 - A15 are programmed externally. When

the routine interval is 8, A0 - A5 are automatically inserted by

the 82C59A while A6 - A15 are programmed externally.

The 8-byte interval will maintain compatibility with current

software, while the 4-byte interval is best for a compact jump

table.

In an 80C86/88/286 system, A15 - A11 are inserted in the

five most significant bits of the vectoring byte and the

82C59A sets the three least significant bits according to the

interrupt level. A10 - A5 are ignored and ADI (Address

interval) has no effect.

LTlM:

If LTlM = 1, then the 82C59A will operate in the level

interrupt mode. Edge detect logic on the interrupt

inputs will be disabled.

ADI:

ALL address interval. ADI = 1 then interval = 4; ADI

= 0 then interval = 8.

SNGL: Single. Means that this is the only 82C59A in the

system. If SNGL = 1, no ICW3 will be issued.

IC4:

If this bit is set - lCW4 has to be issued. If lCW4 is

not needed, set lC4 = 0.

Initialization Command Word 3 (ICW3)

This word is read only when there is more than one 82C59A

in the system and cascading is used, in which case

SNGL = 0. It will load the 8-bit slave register. The functions of

this register are:

a. In the master mode (either when SP = 1, or in buffered

mode when M/S = 1 in lCW4) a “1” is set for each slave in

the bit corresponding to the appropriate IR line for the

slave. The master then will release byte 1 of the call

sequence (for 8080/85 system) and will enable the corre-

sponding slave to release bytes 2 and 3 (for 80C86/88/

286, only byte 2) through the cascade lines.

b. In the slave mode (either when SP = 0, or if BUF = 1 and

M/S = 0 in lCW4), bits 2 - 0 identify the slave. The slave

compares its cascade input with these bits and if they are

equal, bytes 2 and 3 of the call sequence (or just byte 2 for

80C86/88/286) are released by it on the Data Bus.

NOTE: (The slave address must correspond to the IR line it is

connected to in the master ID).

Initialization Command Word 4 (ICW4)

SFNM: If SFNM = 1, the special fully nested mode is pro-

grammed.

BUF:

If BUF = 1, the buffered mode is programmed. In

buffered mode, SP/EN becomes an enable output

and the master/slave determination is by M/S.

M/S:

If buffered mode is selected: M/S = 1 means the

82C59A is programmed to be a master, M/S = 0

means the 82C59A is programmed to be a slave. If

BUF = 0, M/S has no function.

AEOI:

If AEOI = 1, the automatic end of interrupt mode is

programmed.

PM:

Microprocessor mode:

PM = 0 sets the 82C59A for

8080/85 system operation,

PM = 1 sets the

82C59A for 80C86/88/286 system operation.

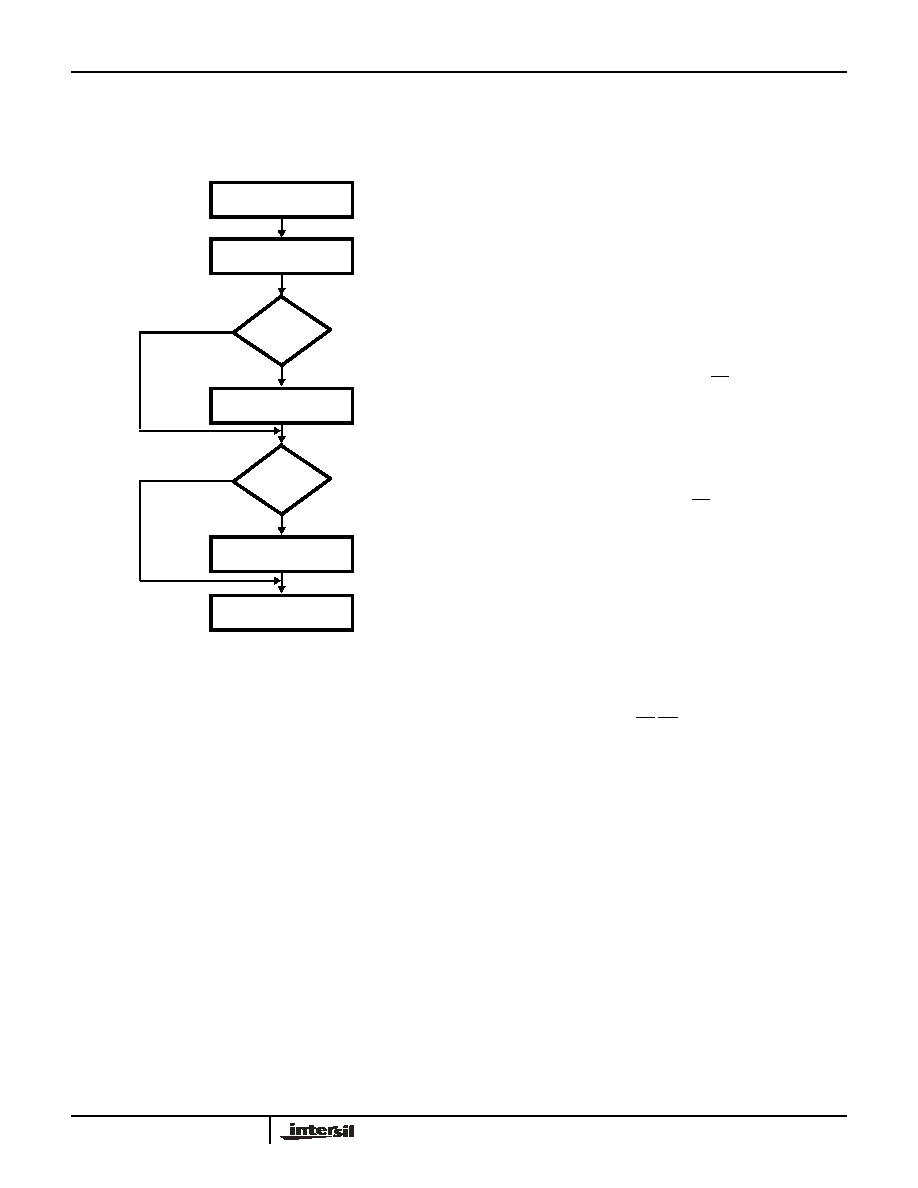

ICW1

ICW2

IN

CASCADE

MODE

ICW3

IS ICW4

NEEDED

ICW4

READY TO ACCEPT

INTERRUPT REQUESTS

NO (SNGL = 1)

YES (SNGL = 0))

YES (IC4 = 1)

NO (IC4 = 0)

FIGURE 6. 82C59A INITIALIZATION SEQUENCE

82C59A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CS8900A-IQZ | IC LAN ETHERNET CTLR 5V 100LQFP |

| CS8952-IQZ | IC TXRX 100/10 PHY 100TQFP |

| CY8CLED04DOCD1-56LTXI | IC POWERPSOC DEBUG 4CH 1A 56VQFN |

| CYG2217 | IC MOD PHONE LINE WIRE 1.07" PCB |

| DAC312ER | IC DAC 12BIT MULT HS 20-CDIP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CS82C59A-12Z | 功能描述:接口 - 專用 W/ANNEAL PERIPH INT CNTRLR 5V 12 5MHZ RoHS:否 制造商:Texas Instruments 產(chǎn)品類型:1080p60 Image Sensor Receiver 工作電源電壓:1.8 V 電源電流:89 mA 最大功率耗散: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:BGA-59 |

| CS82C59A-12Z96 | 功能描述:接口 - 專用 W/ANNEAL PERIPH INT CNTRLR 5V 12 5MHZ RoHS:否 制造商:Texas Instruments 產(chǎn)品類型:1080p60 Image Sensor Receiver 工作電源電壓:1.8 V 電源電流:89 mA 最大功率耗散: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:BGA-59 |

| CS82C59A-5 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS82C59A-5S2064 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS82C59A96 | 功能描述:IC CTRL INTERRUPT 12.5MHZ 28PLCC RoHS:否 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。