- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄170345 > CY38050V256-83BBC (CYPRESS SEMICONDUCTOR CORP) LOADABLE PLD, 15 ns, PBGA256 PDF資料下載

參數(shù)資料

| 型號: | CY38050V256-83BBC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | LOADABLE PLD, 15 ns, PBGA256 |

| 封裝: | 17 X 17 MM, FBGA-256 |

| 文件頁數(shù): | 3/45頁 |

| 文件大小: | 720K |

| 代理商: | CY38050V256-83BBC |

第1頁第2頁當(dāng)前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁

Quantum38K ISR

CPLD Family

Document #: 38-03043 Rev. *G

Page 11 of 45

programming cable is then connected between the PC and

this connector. A simple configuration file instructs the ISR

software of the programming operations to be performed on

the Quantum38K devices in the system. The ISR software

then automatically completes all of the necessary data manip-

ulations required to accomplish configuration, reading,

verifying, and other ISR functions. For more information on the

Cypress ISR interface, see the ISR Programming Kit data

sheet (CY3900i).

The second configuration option for the Quantum38K is to

utilize the embedded controller or processor that already

exists in the system. The Quantum38K ISR software assists in

this method by converting the device HEX file into the ISR

serial stream that contains the ISR instruction information and

the addresses and data of locations to be configured. The

embedded controller then simply directs this ISR stream to the

chain of Quantum38K devices to complete the desired recon-

figuration or diagnostic operations. Contact your local sales

office for information on availability of this option.

Programming

There are multiple methods available for programming the

serial boot PROM. The first method uses Cypress’s

CYDH2200E CPLD Boot PROM Programming Kit to program

via a two-wire interface.

The second method is through third-party programmers.

Programming support for CY3LV series of boot PROMs is

available on a wide variety of third-party programmers. All

major programmers (including BP Micro, Data I/O, System

General, Hi-Lo) support boot PROM programming.

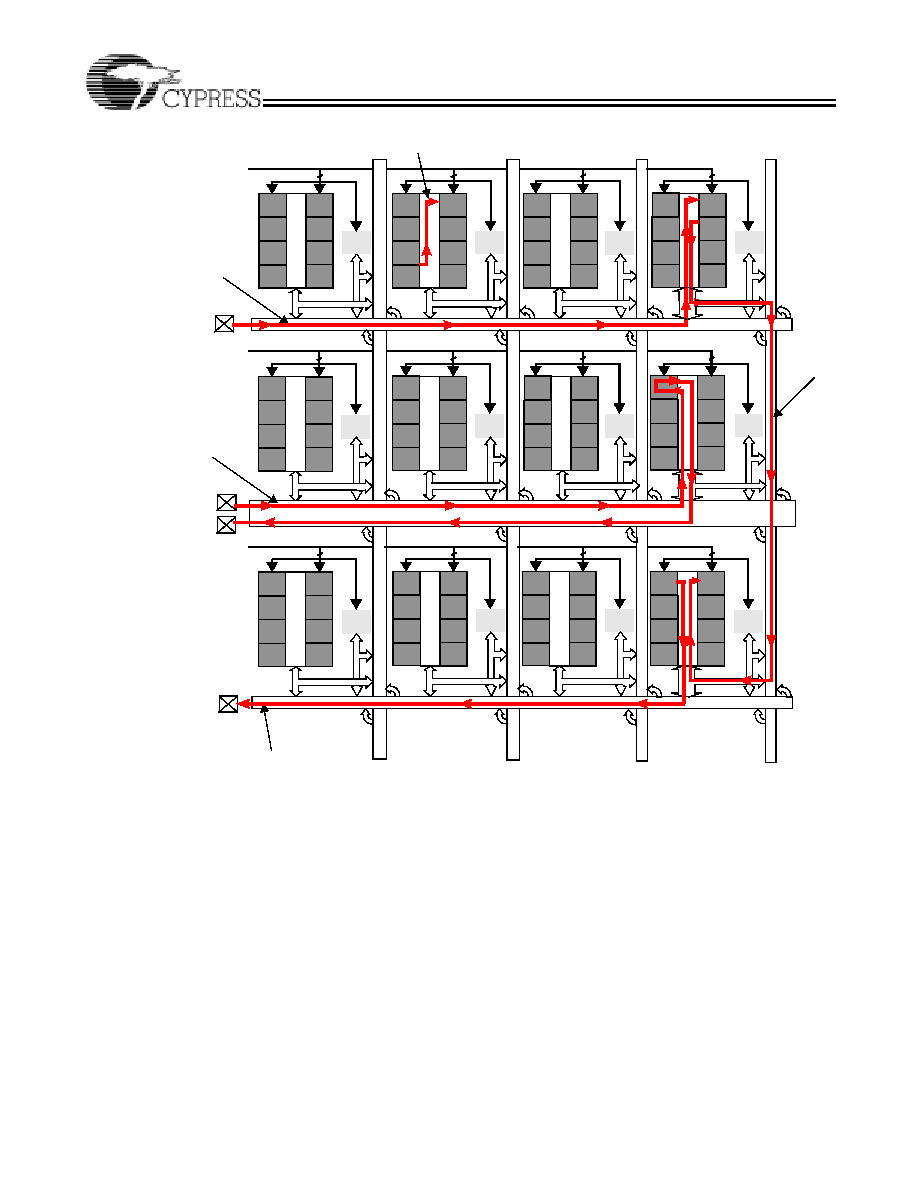

Figure 8. Timing Model for 38K100 Device

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

Channel

RAM

4

GCLK[3:0]

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

Channel

RAM

4

Channel

RAM

4

Channel

RAM

4

Channel

RAM

4

GCLK[3:0]

4

Channel

RAM

4

Channel

RAM

4

GCLK[3:0]

Channel

RAM

4

Channel

RAM

4

Channel

RAM

4

Channel

RAM

Channel

RAM

tMCS

tPD

tSCS

tMCCO

tSCS2

PIM

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY38050V484-83BBC | LOADABLE PLD, 15 ns, PBGA484 |

| CY38050V208-125NC | LOADABLE PLD, 10 ns, PQFP208 |

| CY38050V208-125NI | LOADABLE PLD, 10 ns, PQFP208 |

| CY38050V256-125BBC | LOADABLE PLD, 10 ns, PBGA256 |

| CY38050V256-125BBI | LOADABLE PLD, 10 ns, PBGA256 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY38100V208-125NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 144K GATES 1536 MCRCLLS IND 0.18UM 2.5V/3.3V - Bulk |

| CY3858-000 | 制造商:TE Connectivity 功能描述:2524F0524-1L/9-9-L016 - Cable Rools/Shrink Tubing |

| CY39 | 制造商:PLETRONICS 制造商全稱:Pletronics, Inc. 功能描述:Crystals |

| CY3900I | 功能描述:開發(fā)軟件 ISR Programming Kit RoHS:否 制造商:Atollic Inc. 產(chǎn)品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| CY3900I_05 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:Delta39K⑩⁄Ultra37000⑩ ISR⑩ Programming Kits |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。