- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄295353 > CY7C057V-15AXC (CYPRESS SEMICONDUCTOR CORP) 3.3V 16K/32K x 36 FLEx36™ Asynchronous Dual-Port Static PDF資料下載

參數(shù)資料

| 型號: | CY7C057V-15AXC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | SRAM |

| 英文描述: | 3.3V 16K/32K x 36 FLEx36™ Asynchronous Dual-Port Static |

| 中文描述: | 32K X 36 DUAL-PORT SRAM, 15 ns, PQFP144 |

| 封裝: | 20 X 20 MM, 1.40 MM HEIGHT, ROHS COMPLIANT, PLASTIC, TQFP-144 |

| 文件頁數(shù): | 5/26頁 |

| 文件大?。?/td> | 713K |

| 代理商: | CY7C057V-15AXC |

CY7C056V

CY7C057V

Document #: 38-06055 Rev. *E

Page 13 of 26

Notes

30. R/W must be HIGH during all address transitions.

31. A write occurs during the overlap (tSCE or tPWE) of CE0=VIL and CE1=VIH or SEM=VIL and B0–3 LOW.

32. tHA is measured from the earlier of CE0/CE1 or R/W or (SEM or R/W) going HIGH at the end of Write Cycle.

33. If OE is LOW during a R/W controlled write cycle, the write pulse width must be the larger of tPWE or (tHZWE + tSD) to allow the I/O drivers to turn off and data

to be placed on the bus for the required tSD. If OE is HIGH during an R/W controlled write cycle, this requirement does not apply and the write pulse can be

as short as the specified tPWE.

34. To access RAM, CE0 = VIL, CE1=SEM = VIH.

35. To access byte B0, CE0 = VIL, B0 = VIL, CE1=SEM = VIH.

To access byte B1, CE0 = VIL, B1 = VIL, CE1=SEM = VIH.

To access byte B2, CE0 = VIL, B2 = VIL, CE1=SEM = VIH.

To access byte B3, CE0 = VIL, B3 = VIL, CE1=SEM = VIH.

36. Transition is measured ±150 mV from steady state with a 5-pF load (including scope and jig). This parameter is sampled and not 100% tested.

37. During this period, the I/O pins are in the output state, and input signals must not be applied.

38. If the CE0 LOW and CE1 HIGH or SEM LOW transition occurs simultaneously with or after the R/W LOW transition, the outputs remain in the high-impedance

state.

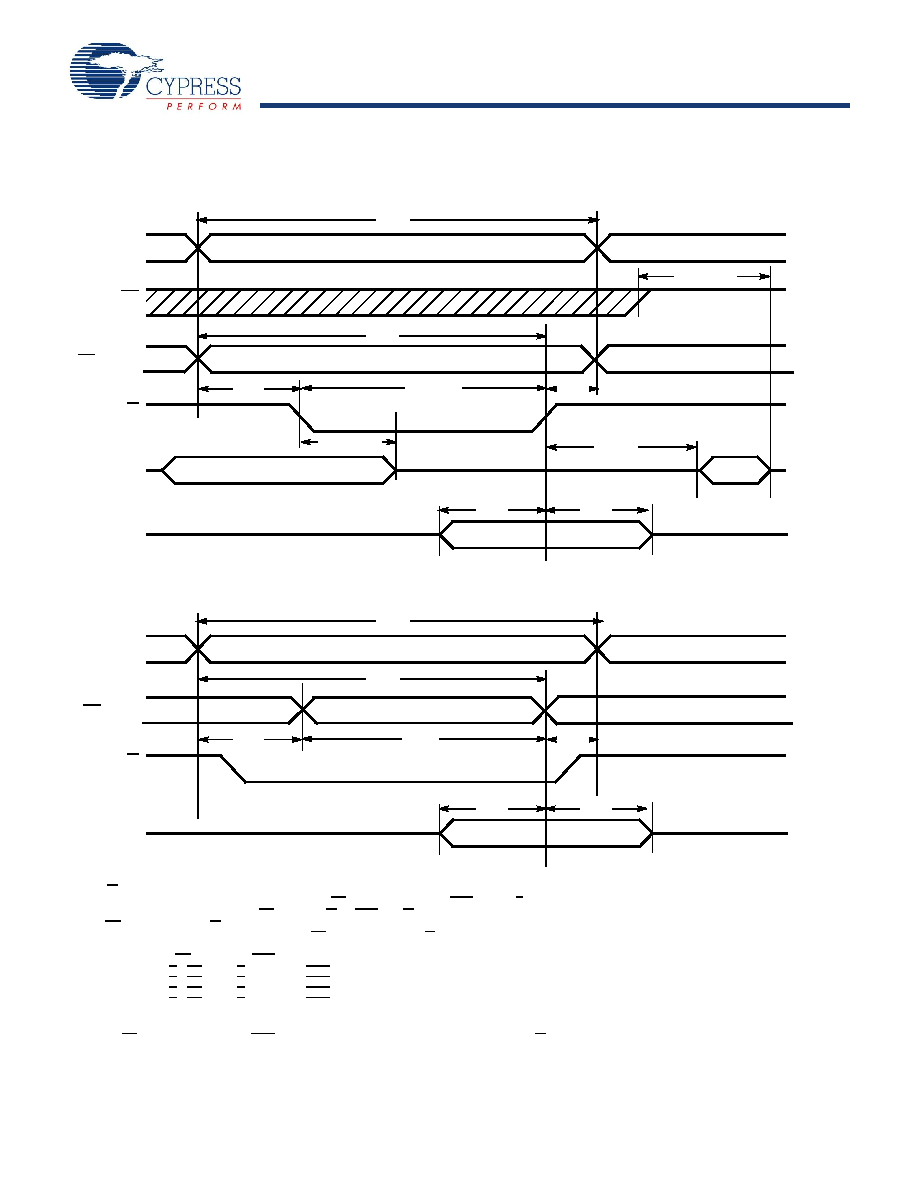

Switching Waveforms (continued)

tAW

tWC

tPWE

tHD

tSD

tHA

CE0, CE1

R/W

OE

DATAOUT

DATA IN

ADDRESS

tHZOE

tSA

tHZWE

tLZWE

Write Cycle No. 1: R/W Controlled Timing[30, 31, 32, 33]

NOTE 37

CHIP SELECT VALID

tAW

tWC

tSCE

tHD

tSD

tHA

R/W

DATA IN

ADDRESS

tSA

Write Cycle No. 2: CE Controlled Timing[30, 31, 32, 38]

CE0, CE1

CHIP SELECT VALID

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C0832V-167AXC | 256K X 18 DUAL-PORT SRAM, 4 ns, PQFP120 |

| CY7C0851AV-133AXC | FLEx36™ 3.3V 32K/64K/128K/256K x 36 Synchronous Dual-Port RAM |

| CY7C0851AV-133BBC | FLEx36™ 3.3V 32K/64K/128K/256K x 36 Synchronous Dual-Port RAM |

| CY7C0851AV-167AXC | FLEx36™ 3.3V 32K/64K/128K/256K x 36 Synchronous Dual-Port RAM |

| CY7C0851AV-167BBC | FLEx36™ 3.3V 32K/64K/128K/256K x 36 Synchronous Dual-Port RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C057V-15AXCT | 功能描述:靜態(tài)隨機存取存儲器 3.3V 16Kx36 Aync COM FLEx36 DualPort 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C057V-15AXI | 功能描述:靜態(tài)隨機存取存儲器 3.3V 16Kx36 Aync IND FLEx36 DualPort 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C057V-15BBC | 功能描述:靜態(tài)隨機存取存儲器 3.3V 16Kx36 Aync COM FLEx36 DualPort 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C057V-15BBI | 功能描述:靜態(tài)隨機存取存儲器 3.3V 16Kx36 Aync IND FLEx36 DualPort 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C057V-15BBXC | 功能描述:靜態(tài)隨機存取存儲器 3.3V 32Kx36 Async FLEx36 Dual Prt 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。