- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄295359 > CY7C1300A Memory PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C1300A |

| 英文描述: | Memory |

| 中文描述: | 內(nèi)存 |

| 文件頁(yè)數(shù): | 4/9頁(yè) |

| 文件大?。?/td> | 194K |

| 代理商: | CY7C1300A |

CY7C1019B/

CY7C10191B

Document #: 38-05026 Rev. *A

Page 4 of 9

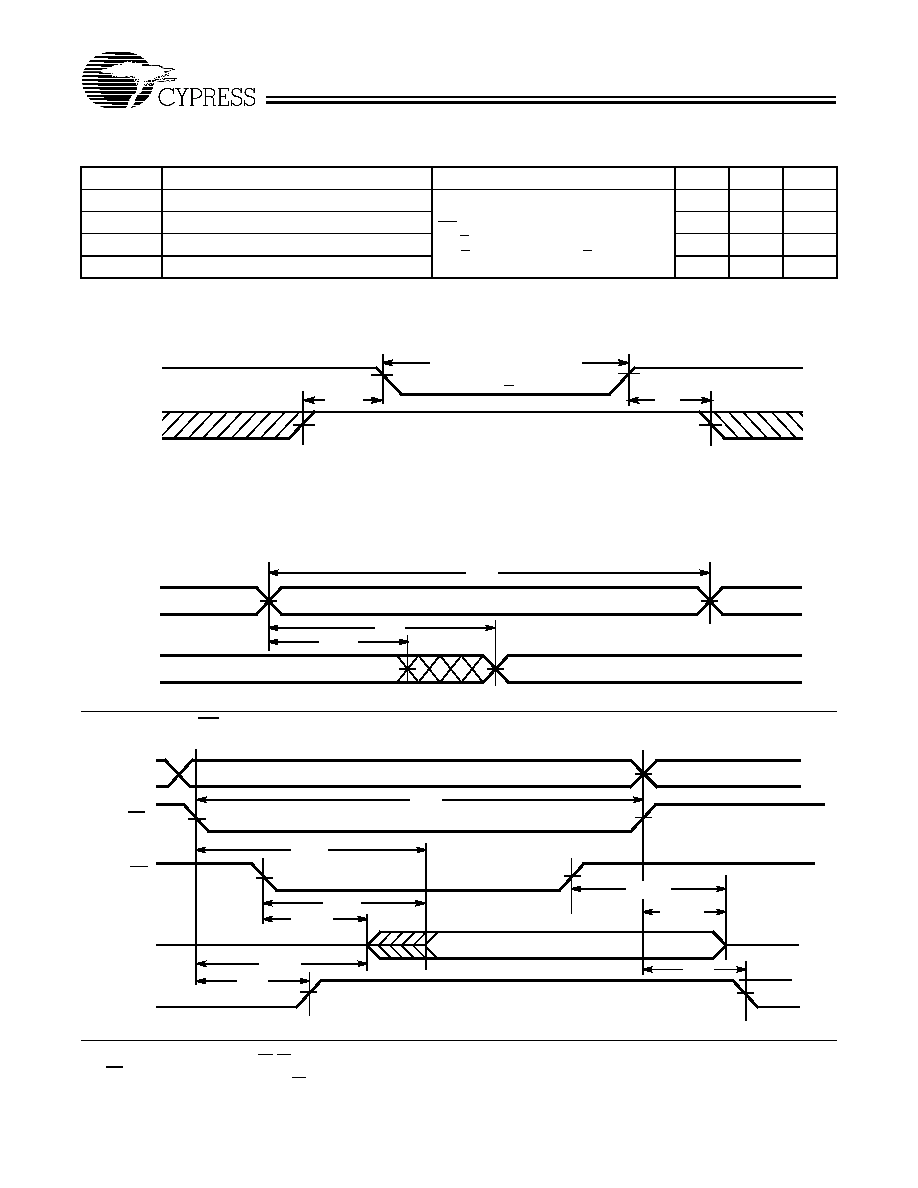

Data Retention Characteristics Over the Operating Range (L Version Only)

Parameter

Description

Conditions

Min.

Max.

Unit

VDR

VCC for Data Retention

No input may exceed VCC + 0.5V

VCC = VDR = 2.0V,

CE > VCC – 0.3V,

VIN > VCC – 0.3V or VIN < 0.3V

2.0

V

ICCDR

Data Retention Current

300

A

tCDR

[3]

Chip Deselect to Data Retention Time

0

ns

tR

Operation Recovery Time

200

s

Data Retention Waveform

3.0V

tCDR

VDR > 2V

DATA RETENTION MODE

tR

CE

VCC

Switching Waveforms

Read Cycle No. 1[9, 10]

Read Cycle No. 2 (OE Controlled)[10, 11]

Notes:

9.

Device is continuously selected. OE, CE = VIL.

10. WE is HIGH for read cycle.

11. Address valid prior to or coincident with CE transition LOW.

PREVIOUS DATA VALID

DATA VALID

tRC

tAA

tOHA

ADDRESS

DATA OUT

50%

DATA VALID

tRC

tACE

tDOE

tLZOE

tLZCE

tPU

HIGH IMPEDANCE

tHZOE

tHZCE

tPD

HIGH

OE

CE

ICC

ISB

IMPEDANCE

ADDRESS

DATA OUT

VCC

SUPPLY

CURRENT

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C1301A | Memory |

| CY7C130-25DC | x8 Dual-Port SRAM |

| CY7C130-25LC | x8 Dual-Port SRAM |

| CY7C130-25PC | x8 Dual-Port SRAM |

| CY7C1302V25 | Memory |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1300A-83AC | 制造商:Cypress Semiconductor 功能描述:SRAM Chip Sync Dual 3.3V 4.5M-Bit 128K x 36 6ns 176-Pin TQFP |

| CY7C1301A WAF | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1302BV25-100BZC | 制造商:Cypress Semiconductor 功能描述:9MB PIPELINE QDR SRAM 2.5V CORE, FBGA, 2 WORD BURST - Trays |

| CY7C1302BV25-133BZC | 制造商:Cypress Semiconductor 功能描述:9MB PIPELINE QDR SRAM 2.5V CORE, FBGA, 2 WORD BURST - Trays |

| CY7C1302BV25-167BZC | 制造商:Cypress Semiconductor 功能描述:9MB PIPELINE QDR SRAM 2.5V CORE, FBGA, 2 WORD BURST - Trays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。