- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378506 > CY7C1412BV18-167BZI (CYPRESS SEMICONDUCTOR CORP) 36-Mbit QDR-II⑩ SRAM 2-Word Burst Architecture PDF資料下載

參數(shù)資料

| 型號: | CY7C1412BV18-167BZI |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | 36-Mbit QDR-II⑩ SRAM 2-Word Burst Architecture |

| 中文描述: | 2M X 18 QDR SRAM, 0.5 ns, PBGA165 |

| 封裝: | 15 X 17 MM, 1.40 MM HEIGHT, MO-216, FBGA-165 |

| 文件頁數(shù): | 22/26頁 |

| 文件大小: | 1072K |

| 代理商: | CY7C1412BV18-167BZI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁

PRELIMINARY

CY7C1410BV18

CY7C1425BV18

CY7C1412BV18

CY7C1414BV18

Document #: 001-07036 Rev. *B

Page 22 of 26

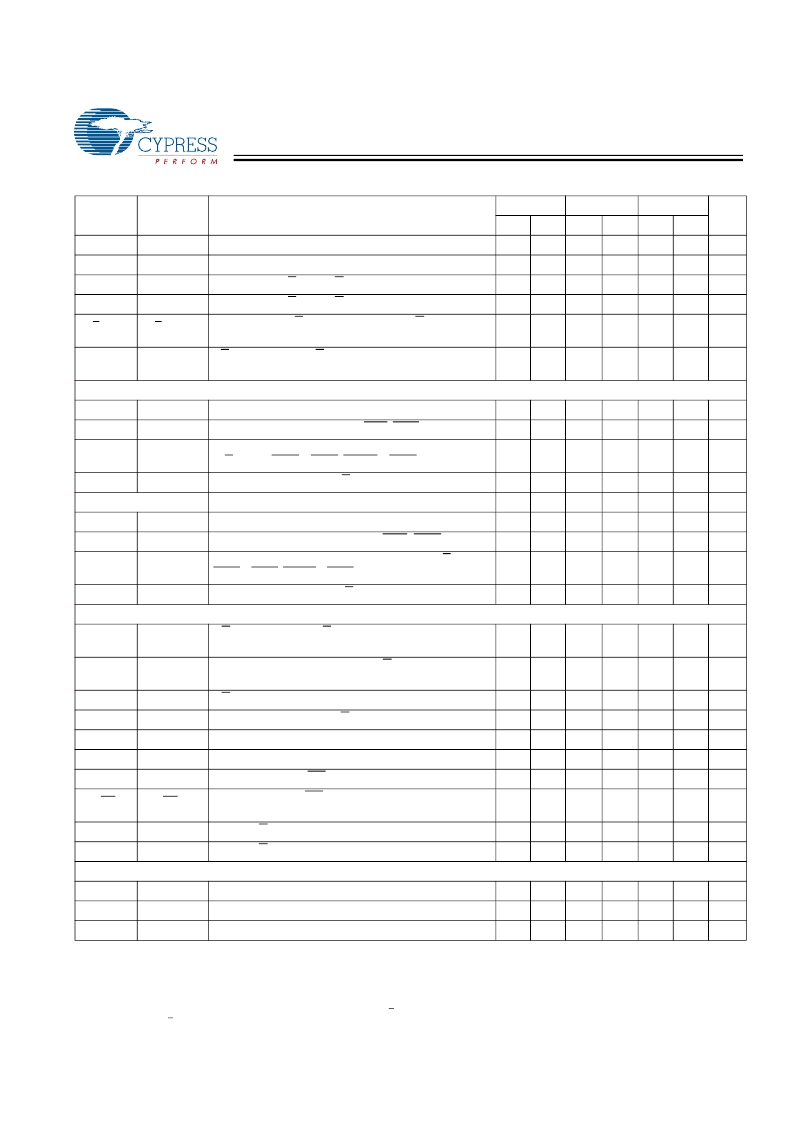

Switching Characteristics

Over the Operating Range

[21, 22]

Cypress

Parameter

t

POWER

t

CYC

t

KH

t

KL

t

KHKH

Consortium

Parameter

Description

250 MHz

Min. Max. Min.

1

4.0

6.3

1.6

–

1.6

–

1.8

–

200 MHz

167 MHz

Unit

ms

ns

ns

ns

ns

Max. Min. Max.

1

7.9

6.0

–

2.4

–

2.4

–

2.7

V

DD

(Typical) to the first Access

[23]

K Clock and C Clock Cycle Time

Input Clock (K/K and C/C) HIGH

Input Clock (K/K and C/C) LOW

K Clock Rise to K Clock Rise and C to C Rise (rising

edge to rising edge)

K/K Clock Rise to C/C Clock Rise (rising edge to rising

edge)

1

t

KHKH

t

KHKL

t

KLKH

t

KHKH

5.0

2.0

2.0

2.2

8.4

–

–

–

t

KHCH

t

KHCH

0

1.8

0

2.2

0

2.7

ns

Set-up Times

t

SA

t

SC

t

SCDDR

t

AVKH

t

IVKH

t

IVKH

Address Set-up to K Clock Rise

Control Set-up to K Clock Rise (RPS, WPS)

Double Data Rate Control Set-up to Clock

(K/K) Rise (BWS

0

, BWS

1

, BWS

3

, BWS

4

)

D

[X:0]

Set-up to Clock (K/K) Rise

0.35

0.35

0.35

–

–

–

0.4

0.4

0.4

–

–

–

0.5

0.5

0.5

–

–

–

ns

ns

ns

t

SD[24]

Hold Times

t

HA

t

HC

t

HCDDR

t

DVKH

0.35

–

0.4

–

0.5

–

ns

t

KHAX

t

KHIX

t

KHIX

Address Hold after K Clock Rise

Control Hold after K Clock Rise (RPS, WPS)

Double Data Rate Control Hold after Clock (K/K) Rise

(BWS

0

, BWS

1

, BWS

3

, BWS

4

)

D

[X:0]

Hold after Clock (K/K) Rise

0.35

0.35

0.35

–

–

–

0.4

0.4

0.4

–

–

–

0.5

0.5

0.5

–

–

–

ns

ns

ns

t

HD

Output Times

t

CO

t

KHDX

0.35

–

0.4

–

0.5

–

ns

t

CHQV

C/C Clock Rise (or K/K in Single Clock Mode) to Data

Valid

Data Output Hold after Output C/C Clock Rise (Active

to Active)

C/C Clock Rise to Echo Clock Valid

Echo Clock Hold after C/C Clock Rise

Echo Clock High to Data Valid

Echo Clock High to Data Invalid

Output Clock (CQ/CQ) HIGH

[25]

CQ Clock Rise to CQ Clock Rise

[25]

(rising edge to rising edge)

Clock (C/C) Rise to High-Z (Active to High-Z)

[26,27]

Clock (C/C) Rise to Low-Z

[26,27]

–

0.45

–

0.45

–

0.50

ns

t

DOH

t

CHQX

–0.45

–

-0.45

–

-0.50

–

ns

t

CCQO

t

CQOH

t

CQD

t

CQDOH

t

CQH

t

CQHCQH

t

CHCQV

t

CHCQX

t

CQHQV

t

CQHQX

t

CQHCQL

t

CQHCQH

–

0.45

–

0.30

–

–

–

–

0.45

–

0.35

–

–

–

–

0.50

–

0.40

–

–

–

ns

ns

ns

ns

ns

ns

–0.45

–

–0.30

1.55

1.55

–0.45

–

–0.35

1.95

1.95

–0.50

–

–0.40

2.45

2.45

t

CHZ

t

CLZ

DLL Timing

t

KC Var

t

KC lock

t

KC Reset

Notes:

22.All devices can operate at clock frequencies as low as 119 MHz. When a part with a maximum frequency above 133 MHz is operating at a lower clock frequency,

it requires the input timings of the frequency range in which it is being operated and will output data with the output timings of that frequency range.

23.This part has a voltage regulator internally; t

POWER

is the time that the power needs to be supplied above V

DD

minimum initially before a read or write operation

can be initiated.

24.For D2 data signal on CY7C1425BV18 device, t

is 0.5ns for 200MHz, and 250MHz frequencies.

25.These parameters are extrapolated from the input timing parameters (t

- 250 ps, where 250 ps is the internal jitter. An input jitter of 200 ps (t

KC Var

) ia already

included in the t

). These parameters are only guaranteed by design and are not tested in production.

26.t

, t

, are specified with a load capacitance of 5 pF as in part (b) of AC Test Loads. Transition is measured

±

100 mV from steady-state voltage.

27.At any given voltage and temperature t

CHZ

is less than t

CLZ

and t

CHZ

less than t

CO

.

t

CHQZ

t

CHQX1

–

0.45

–

–

0.45

–

–

0.50

–

ns

ns

–0.45

–0.45

–0.50

t

KC Var

t

KC lock

t

KC Reset

Clock Phase Jitter

DLL Lock Time (K, C)

K Static to DLL Reset

–

0.20

–

–

–

0.20

–

–

–

0.20

–

–

ns

1024

30

1024

30

1024

30

cycles

ns

[+] Feedback

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C1412BV18-167BZXI | 36-Mbit QDR-II⑩ SRAM 2-Word Burst Architecture |

| CY7C1414BV18 | 36-Mbit QDR-II⑩ SRAM 2-Word Burst Architecture |

| CY7C1414BV18-167BZI | 36-Mbit QDR-II⑩ SRAM 2-Word Burst Architecture |

| CY7C1414BV18-167BZXI | 36-Mbit QDR-II⑩ SRAM 2-Word Burst Architecture |

| CY7C1411AV18-167BZC | 36-Mbit QDR⑩-II SRAM 4-Word Burst Architecture |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1412BV18-167BZXI | 功能描述:靜態(tài)隨機存取存儲器 2Mx18 QDR II Burst 2 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1412BV18-200BZC | 功能描述:靜態(tài)隨機存取存儲器 2Mx18 QDR II Burst 2 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1412BV18-200BZI | 功能描述:靜態(tài)隨機存取存儲器 2Mx18 QDR-II Burst 2 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1412BV18-200BZXC | 功能描述:靜態(tài)隨機存取存儲器 2Mx18 QDR-II Burst 2 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1412BV18-200BZXI | 制造商:Cypress Semiconductor 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。