- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379060 > CY7C143-25JI (CYPRESS SEMICONDUCTOR CORP) 2K x 16 Dual-Port Static RAM PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C143-25JI |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | 2K x 16 Dual-Port Static RAM |

| 中文描述: | 2K X 16 DUAL-PORT SRAM, 25 ns, PQCC68 |

| 封裝: | PLASTIC, LCC-68 |

| 文件頁數(shù): | 7/13頁 |

| 文件大小: | 506K |

| 代理商: | CY7C143-25JI |

CY7C133

CY7C143

Document #: 38-06036 Rev. *B

Page 7 of 13

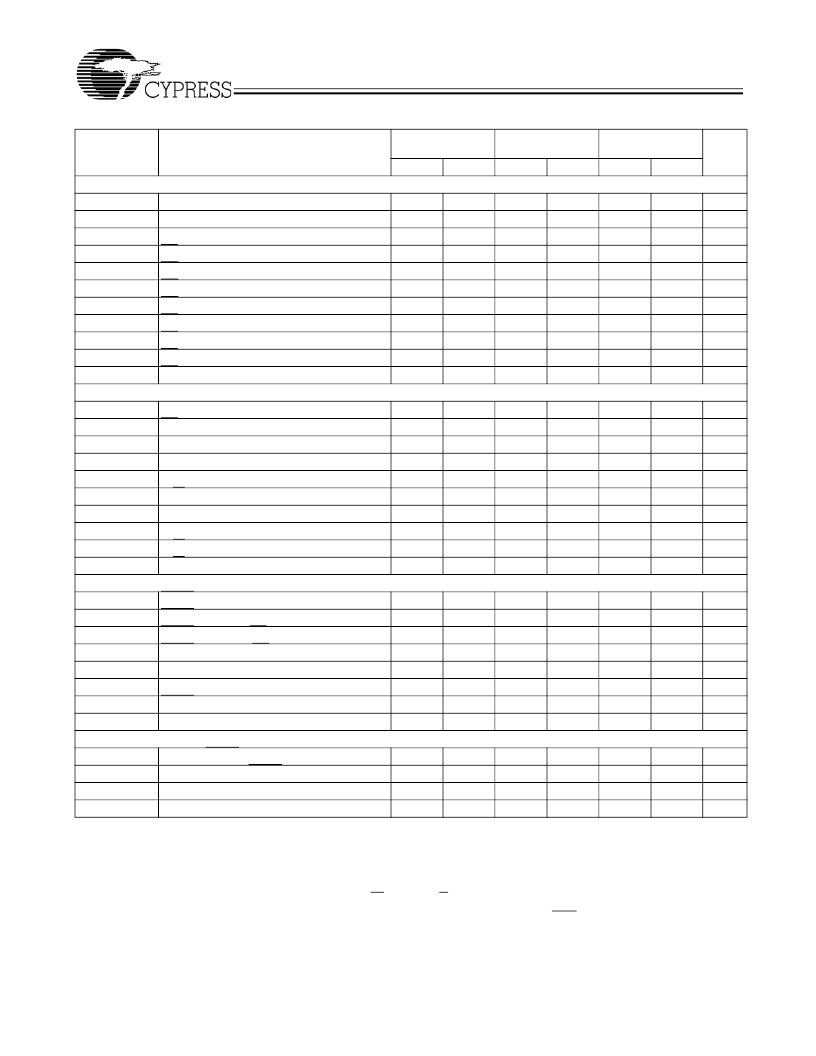

Switching Characteristics

Over the Operating Range

[9]

Parameter

Read Cycle

t

RC

t

AA

t

OHA

t

ACE

t

DOE

t

LZOE

t

HZOE

t

LZCE

t

HZCE

t

PU

t

PD

Write Cycle

[14]

t

WC

t

SCE

t

AW

t

HA

t

SA

t

PWE

t

SD

t

HD

t

HZWE

t

LZWE

Busy/Interrupt Timing (for master CY7C133)

t

BLA

BUSY Low from Address Match

t

BHA

BUSY High from Address Mismatch

t

BLC

BUSY Low from CE LOW

t

BHC

BUSY High from CE HIGH

t

WDD

t

DDD

t

BDD

t

PS

Busy Timing (for slave CY7C143)

t

WB

t

WH

t

WDD

t

DDD

Notes:

9.

Test conditions assume signal transition times of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V and output loading of the specified

I

/I

and 30-pF load capacitance.

10. AC Test Conditions use V

= 1.6V and V

= 1.4V.

11.

At any given temperature and voltage condition for any given device, t

is less than t

and t

is less than t

.

12. t

, t

, t

, t

, t

and t

are tested with C

L

= 5 pF as in part (b) of AC Test Loads

.

Transition is measured ±500 mV from steady state voltage.

13. This parameter is guaranteed but not tested.

14. The internal write time of the memory is defined by the overlap of CS LOW and R/W LOW. Both signals must be LOW to initiate a write and either signal

can terminate a write by going HIGH. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the write.

15. Port-to-port delay through RAM cells from writing port to reading port. Refer to timing waveform of “Read with BUSY, Master: CY7C133.”

16. t

is a calculated parameter and is greater of 0,t

WDD

–t

WP

(actual) or t

DDD

–t

DW

(actual).

17. To ensure that the earlier of the two ports wins.

18. To ensure that write cycle is inhibited during contention.

19. To ensure that a write cycle is completed after contention.

20. Port-to-port delay through RAM cells from writing port to reading port. Refer to timing waveform of “Read with Port-to-port Delay.”

Description

7C133-25

7C143-25

Min.

7C133-35

7C143-35

Min.

7C133-55

7C143-55

Min.

Unit

Max.

Max.

Max.

Read Cycle Time

Address to Data Valid

[10]

Data Hold from Address Change

CE LOW to Data Valid

[10]

OE LOW to Data Valid

[10]

OE LOW to Low Z

[11, 12,13]

OE HIGH to High Z

[11, 12,13]

CE LOW to Low Z

[11, 12,13]

CE HIGH to High Z

[11, 12,13]

CE LOW to Power-Up

[13]

CE HIGH to Power-Down

[13]

25

35

55

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

25

35

55

0

0

0

25

20

35

25

55

30

3

3

3

15

20

25

3

5

5

15

20

20

0

0

0

25

25

25

Write Cycle Time

CE LOW to Write End

Address Set-up to Write End

Address Hold from Write End

Address Set-up to Write Start

R/W Pulse Width

Data Set-up to Write End

Data Hold from Write End

R/W LOW to High Z

[12,13]

R/W HIGH to Low Z

[12,13]

25

20

20

2

0

20

15

0

35

25

25

2

0

25

20

0

55

40

40

2

0

35

20

0

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

15

20

20

0

0

0

25

20

20

20

50

35

35

30

25

20

60

45

50

40

35

30

80

55

ns

ns

ns

ns

ns

ns

ns

ns

Write Pulse to Data Delay

[15]

Write Data Valid to Read Data Valid

[15]

BUSY High to Valid Data

[16]

Arbitration Priority Set Up Time

[17]

Note 16

Note 16

Note 16

5

5

5

Write to BUSY

[18]

Write Hold After BUSY

[19]

Write Pulse to Data Delay

[20]

Write Data Valid to Read Data Valid

[20]

0

0

0

ns

ns

ns

ns

20

25

30

50

35

60

45

80

55

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C143-35JC | 2K x 16 Dual-Port Static RAM |

| CY7C143-35JI | 2K x 16 Dual-Port Static RAM |

| CY7C143-55JC | 2K x 16 Dual-Port Static RAM |

| CY7C143-55JI | 2K x 16 Dual-Port Static RAM |

| CY7C1332 | 64K x 18 Synchronous Cache 3.3V RAM(3.3V 64K x 18 同步高速緩沖存儲(chǔ)器 RAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C143-55JC | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Cypress Semiconductor 功能描述: |

| CY7C1440AV25-167BZXC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 36MB (1Mx36) 2.5v 167MHz Sync 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1440AV25-250BZXI | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 36MB (1Mx36) 2.5v 250MHz Sync 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1440AV25-250BZXIT | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1440AV33-167AXC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 1Mx36 3.3V Sync PL 靜態(tài)隨機(jī)存取存儲(chǔ)器 COM RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。