- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376558 > DAC6574EVM (Texas Instruments, Inc.) DAC6574 Evaluation Module(DAC6574評估模塊) PDF資料下載

參數(shù)資料

| 型號: | DAC6574EVM |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | DAC6574 Evaluation Module(DAC6574評估模塊) |

| 中文描述: | DAC6574評估模塊(DAC6574評估模塊) |

| 文件頁數(shù): | 32/39頁 |

| 文件大?。?/td> | 437K |

| 代理商: | DAC6574EVM |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

EVM Stacking

3-4

3.3

EVM Stacking

EVM stacking enables the designer to evaluate two DACx574s in tandem to

yield an eight channel output, or two DACx571s, or two DAC8571s. Any

combination of the seven may be used provided the outputs do not collide. A

maximum of two DACx574 EVMs are allowed since the output terminal, J4,

dictates the number of DAC channels that can be connected without colliding.

For the DACx571 and DAC8571, more than two EVMs can be stacked

together provided the I

2

C address of each stacked EVMs are unique, as the

outputs can be monitored through TP1 instead of shorting W2 jumper and

routing the DAC output to J4. Table 4 shows how the DAC output channels are

mapped into the output terminal, J4, with respect to the jumper position of W2,

W11, W12, and W13.

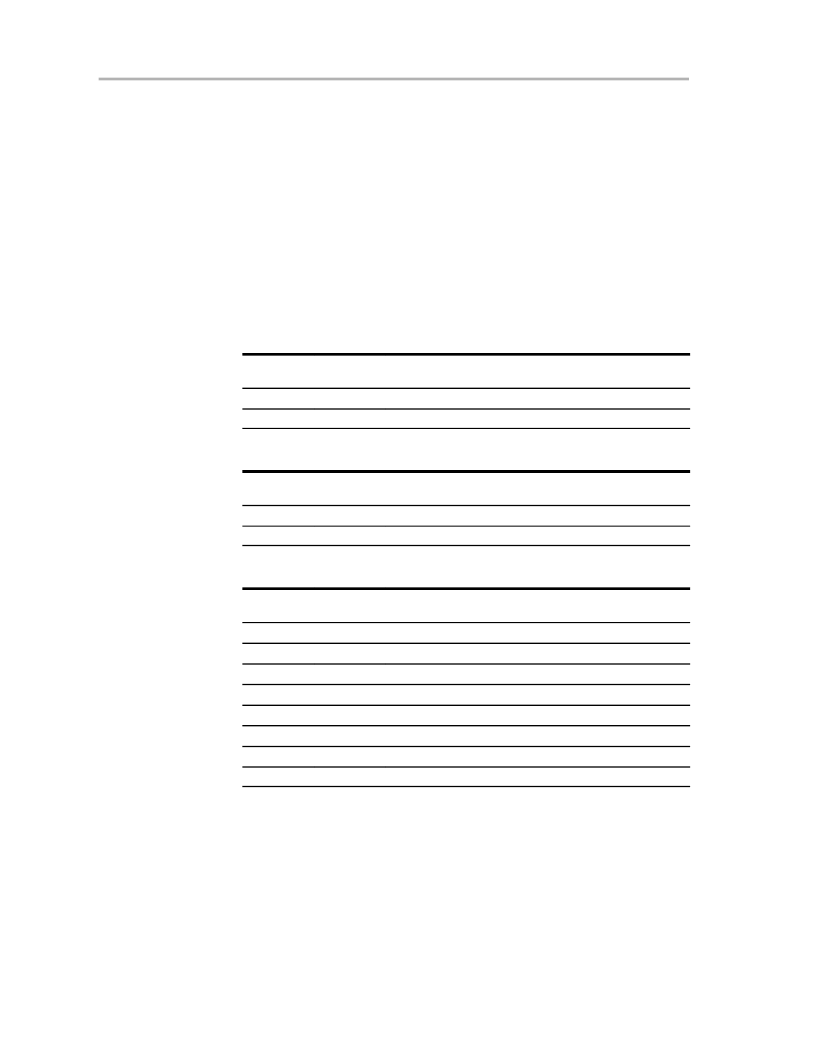

Table 3-4.DAC7571/DAC6571/DAC5571 Output Channel Mapping

Reference

Jumper

Position

1-2

Function

W2

U8 output (V

OUT

) is routed to J4-2.

U8 output (V

OUT

) is routed to J4-10.

2-3

Table 3-5.DAC8571 Output Channel Mapping

Reference

Jumper

Position

1-2

Function

W2

U4 output (V

OUT

) is routed to J4-2.

U4 output (V

OUT

) is routed to J4-10.

2-3

Table 3-6.DAC7574/DAC6574/DAC5574 Output Channel Mapping

Reference

Jumper

Position

1-2

Function

W2

U1 output A (V

OUT

A) is routed to J4-2.

U1 output A (V

OUT

A) is routed to J4-10.

U1 output B (V

OUT

B) is routed to J4-4.

U1 output B (V

OUT

B) is routed to J4-12.

U1 output C (V

OUT

C) is routed to J4-6.

U1 output C (V

OUT

C) is routed to J4-14.

U1 output D (V

OUT

D) is routed to J4-8.

U1 output D (V

OUT

D) is routed to J4-16.

2-3

W11

1-2

2-3

W12

1-2

2-3

W13

1-2

2-3

Each DAC EVM in a stacked configuration must have a unique I

2

C address.

This is accomplished by configuring the address jumpers W7 and W8 (refer

to the datasheet for I

2

C addressing) for the DACx574 EVM. The DACx571 and

DAC8571 use pullup and pulldown resistors R13, R22, R2, and R23

respectively. The table below shows the I

2

C address settings of each EVM.

The cells shaded in gray are factory preset and cannot be changed.

相關PDF資料 |

PDF描述 |

|---|---|

| DAC7574EVM | DAC7574 Evaluation Module(DAC7574評估模塊) |

| DAC5571EVM | DAC5571 Evaluation Module(DAC5571評估模塊) |

| DAC6571EVM | DAC6571 Evaluation Module(DAC6571評估模塊) |

| DAC7571EVM | DAC7571 Evaluation Module(DAC7571評估模塊) |

| DAC56 | Monolithic 16-Bit Resolution DIGITAL-TO-ANALOG CONVERTER |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| DAC6574IDGS | 功能描述:數(shù)模轉換器- DAC 10-bit Quad w/I2C interface RoHS:否 制造商:Texas Instruments 轉換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| DAC6574IDGSG4 | 功能描述:數(shù)模轉換器- DAC 10-bit Quad w/I2C interface RoHS:否 制造商:Texas Instruments 轉換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| DAC6574IDGSR | 功能描述:數(shù)模轉換器- DAC 10-bit Quad w/I2C interface RoHS:否 制造商:Texas Instruments 轉換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| DAC6574IDGSRG4 | 功能描述:數(shù)模轉換器- DAC 10-bit Quad w/I2C interface RoHS:否 制造商:Texas Instruments 轉換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| DAC6578 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:8-/10-/12-Bit, Octal-Channel, Ultra-Low Glitch, Voltage Output, Two-Wire Interface Digital-to-Analog Converters |

發(fā)布緊急采購,3分鐘左右您將得到回復。