- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄295418 > DAC7512E/250 (TEXAS INSTRUMENTS INC) SERIAL INPUT LOADING, 8 us SETTLING TIME, 12-BIT DAC, PDSO8 PDF資料下載

參數(shù)資料

| 型號: | DAC7512E/250 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | DAC |

| 英文描述: | SERIAL INPUT LOADING, 8 us SETTLING TIME, 12-BIT DAC, PDSO8 |

| 封裝: | GREEN, PLASTIC, MSOP-8 |

| 文件頁數(shù): | 4/23頁 |

| 文件大?。?/td> | 1094K |

| 代理商: | DAC7512E/250 |

DAC7512

12

SBAS156B

www.ti.com

DB13

DB12

OPERATING MODE

0

Normal Operation

Power-Down Modes:

0

1

Output 1k

to GND

1

0

Output 100k

to GND

1

High-Z

TABLE I. Modes of Operation for the DAC7512.

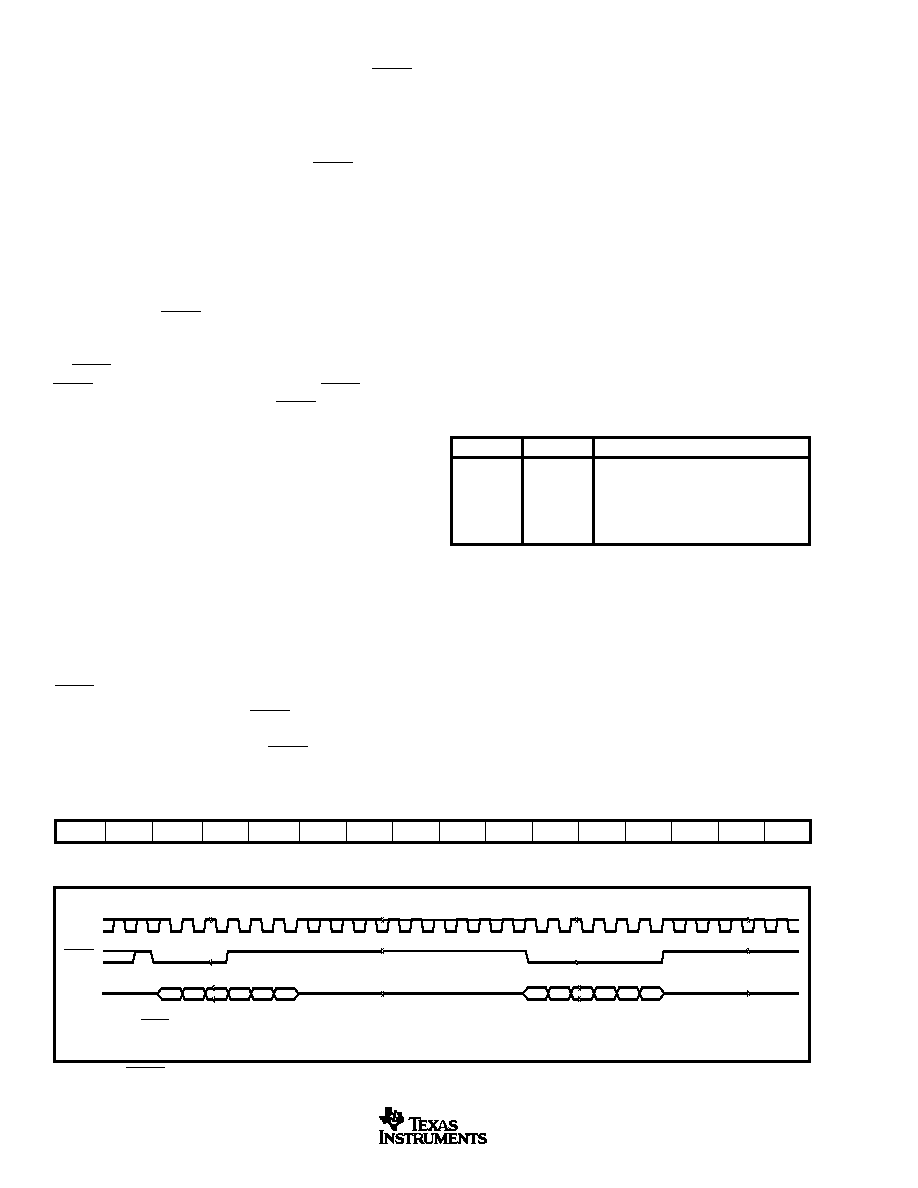

FIGURE 4. SYNC Interrupt Facility.

CLK

SYNC

D

IN

Invalid Write Sequence:

SYNC HIGH before 16th Falling Edge

Valid Write Sequence: Output Updates

on the 16th Falling Edge

DB15

DB0

DB15

DB0

SERIAL INTERFACE

The DAC7512 has a three-wire serial interface (SYNC,

SCLK, and DIN), which is compatible with SPI, QSPI, and

Microwire interface standards as well as most Digital Signal

Processors (DSPs). See the Serial Write Operation timing

diagram for an example of a typical write sequence.

The write sequence begins by bringing the SYNC line LOW.

Data from the DIN line is clocked into the 16-bit shift register

on the falling edge of SCLK. The serial clock frequency can

be as high as 30MHz, making the DAC7512 compatible with

high-speed DSPs. On the 16th falling edge of the serial

clock, the last data bit is clocked in and the programmed

function is executed (i.e., a change in DAC register contents

and/or a change in the mode of operation).

At this point, the SYNC line may be kept LOW or brought

HIGH. In either case, it must be brought HIGH for a minimum

of 33ns before the next write sequence so that a falling edge

of SYNC can initiate the next write sequence. Since the

SYNC buffer draws more current when the SYNC signal is

HIGH than it does when it is LOW, SYNC should be idled

LOW between write sequences for lowest power operation of

the part. As mentioned above, however, it must be brought

HIGH again just before the next write sequence.

INPUT SHIFT REGISTER

The input shift register is 16 bits wide, as shown in Figure 3.

The first two bits are “don’t cares”. The next two bits (PD1

and PD0) are control bits that control which mode of opera-

tion the part is in (normal mode or one of three power-down

modes). There is a more complete description of the various

modes in the Power-Down Modes section. The next 12 bits

are the data bits. These are transferred to the DAC register

on the 16th falling edge of SCLK.

SYNC INTERRUPT

In a normal write sequence, the SYNC line is kept LOW for

at least 16 falling edges of SCLK and the DAC is updated on

the 16th falling edge. However, if SYNC is brought HIGH

before the 16th falling edge, this acts as an interrupt to the

write sequence. The shift register is reset and the write

sequence is seen as invalid. Neither an update of the DAC

register contents or a change in the operating mode occurs,

as shown in Figure 4.

POWER-ON RESET

The DAC7512 contains a power-on reset circuit that controls

the output voltage during power-up. On power-up, the DAC

register is filled with zeros and the output voltage is 0V; it

remains there until a valid write sequence is made to the

DAC. This is useful in applications where it is important to

know the state of the output of the DAC while it is in the

process of powering up.

POWER-DOWN MODES

The DAC7512 contains four separate modes of operation.

These modes are programmable by setting two bits (PD1

and PD0) in the control register. Table I shows how the state

of the bits corresponds to the mode of operation of the

device.

DB15

DB0

X

PD1

PD0

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

FIGURE 3. Data Input Register.

When both bits are set to 0, the part works normally with its

normal power consumption of 135A at 5V. However, for the

three power-down modes, the supply current falls to 200nA

at 5V (50nA at 3V). Not only does the supply current fall, but

the output stage is also internally switched from the output of

the amplifier to a resistor network of known values. This has

the advantage that the output impedance of the part is known

while the part is in power-down mode. There are three

different options. The output is connected internally to GND

through a 1k

resistor, a 100k resistor, or it is left open-

circuited (High-Z). See Figure 5 for the output stage.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DAC7512N/3K | SERIAL INPUT LOADING, 8 us SETTLING TIME, 12-BIT DAC, PDSO6 |

| DAC7631EB | SERIAL INPUT LOADING, 8 us SETTLING TIME, 16-BIT DAC, PDSO20 |

| DAC7631E | SERIAL INPUT LOADING, 8 us SETTLING TIME, 16-BIT DAC, PDSO20 |

| DAC7631E/1KG4 | SERIAL INPUT LOADING, 8 us SETTLING TIME, 16-BIT DAC, PDSO20 |

| DAC8830IBDG4 | SERIAL INPUT LOADING, 1 us SETTLING TIME, 16-BIT DAC, PDSO8 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DAC7512N | 制造商:Texas Instruments 功能描述: |

| DAC7512N/250 | 功能描述:數(shù)模轉(zhuǎn)換器- DAC Lo-Pwr R-To-R Output 12-Bit Serial Input RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| DAC7512N/250G4 | 功能描述:數(shù)模轉(zhuǎn)換器- DAC Lo-Pwr R-To-R Output 12-Bit Serial Input RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| DAC7512N/3K | 功能描述:數(shù)模轉(zhuǎn)換器- DAC Lo-Pwr R-To-R Output 12-Bit Serial Input RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| DAC7512N/3KG4 | 功能描述:數(shù)模轉(zhuǎn)換器- DAC Lo-Pwr R-To-R Output 12-Bit Serial Input RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。