- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376797 > DM74LS73AM (FAIRCHILD SEMICONDUCTOR CORP) Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops with Clear and Complementary Outputs PDF資料下載

參數(shù)資料

| 型號: | DM74LS73AM |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 通用總線功能 |

| 英文描述: | Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops with Clear and Complementary Outputs |

| 中文描述: | LS SERIES, DUAL NEGATIVE EDGE TRIGGERED J-K FLIP-FLOP, COMPLEMENTARY OUTPUT, PDSO14 |

| 封裝: | 0.150 INCH, MS-120, SOIC-14 |

| 文件頁數(shù): | 2/5頁 |

| 文件大小: | 53K |

| 代理商: | DM74LS73AM |

www.fairchildsemi.com

2

D

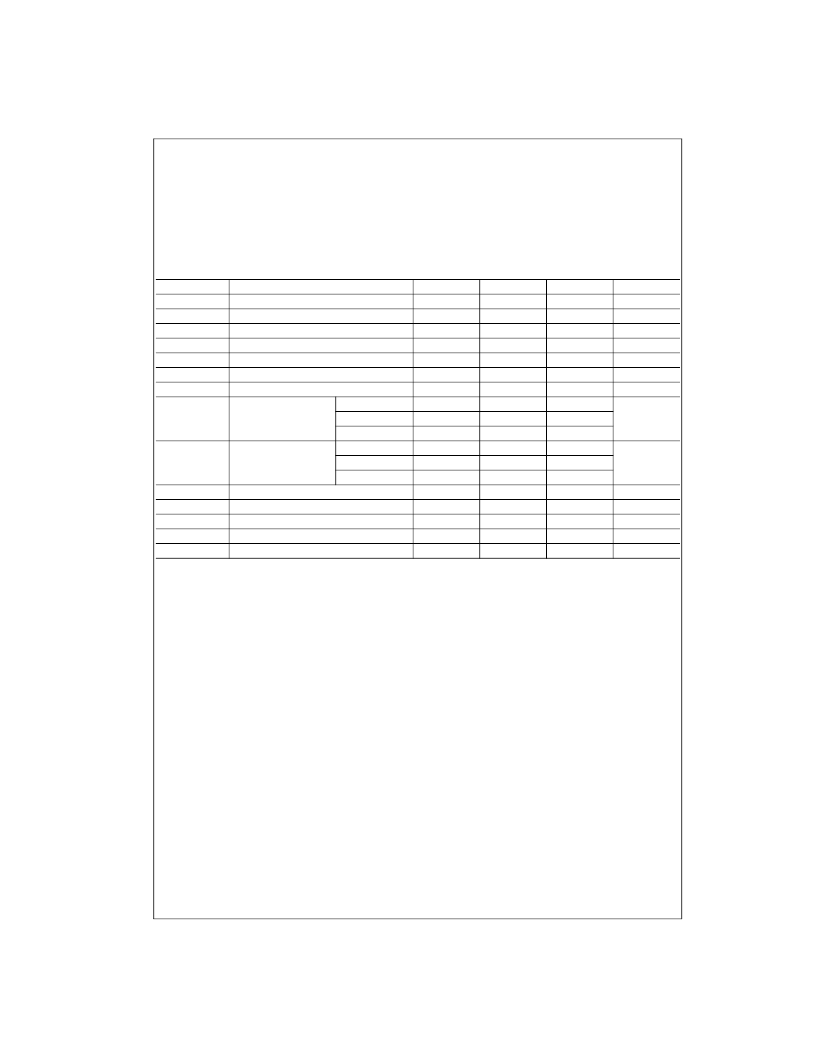

Absolute Maximum Ratings

(Note 1)

Note 1:

The “Absolute Maximum Ratings” are those values beyond which

the safety of the device cannot be guaranteed. The device should not be

operated at these limits. The parametric values defined in the Electrical

Characteristics tables are not guaranteed at the absolute maximum ratings.

The “Recommended Operating Conditions” table will define the conditions

for actual device operation.

Recommended Operating Conditions

Note 2:

C

L

=

15 pF, R

L

=

2 k

, T

A

=

25

°

C and V

CC

=

5V.

Note 3:

C

L

=

50 pF, R

L

=

2 k

, T

A

=

25

°

C and V

CC

=

5V.

Note 4:

The symbol (

↓

) indicates the falling edge of the clock pulse is used for reference.

Supply Voltage

Input Voltage

Operating Free Air Temperature Range

Storage Temperature Range

7V

7V

0

°

C to

+

70

°

C

65

°

C to

+

150

°

C

Symbol

Parameter

Min

4.75

2

Nom

5

Max

5.25

Units

V

V

V

mA

mA

MHz

MHz

V

CC

V

IH

V

IL

I

OH

I

OL

f

CLK

f

CLK

t

W

Supply Voltage

HIGH Level Input Voltage

LOW Level Input Voltage

HIGH Level Output Current

LOW Level Output Current

Clock Frequency (Note 2)

Clock Frequency (Note 3)

Pulse Width

(Note 2)

0.8

0.4

8

30

25

0

0

20

25

25

25

30

30

20

↓

25

↓

0

↓

5

↓

0

Clock HIGH

Preset LOW

Clear LOW

Clock HIGH

Preset LOW

Clear LOW

ns

t

W

Pulse Width

(Note 3)

ns

t

SU

t

SU

t

H

t

H

T

A

Setup Time (Note 2)(Note 4)

Setup Time (Note 3)(Note 4)

Hold Time (Note 2)(Note 4)

Hold Time (Note 3)(Note 4)

Free Air Operating Temperature

ns

ns

ns

ns

°

C

70

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM74LS73AN | Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops with Clear and Complementary Outputs |

| DM74LS73AMX | J-K-Type Flip-Flop |

| DM74LS74A | Dual Positive-Edge-Triggered D Flip-Flops with Preset, Clear and Complementary Outputs(帶清零和互補(bǔ)輸出的雙負(fù)邊緣觸發(fā)的主-從J-K觸發(fā)器) |

| DM74LS74 | Dual Positive-Edge-Triggered D Flip-Flops with Preset, Clear and Complementary Outputs |

| DM74LS74AM | Dual Positive-Edge-Triggered D Flip-Flops with Preset, Clear and Complementary Outputs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM74LS73AN | 功能描述:觸發(fā)器 Dual J-K Flip-Flop RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時(shí)間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| DM74LS74 WAF | 制造商:Texas Instruments 功能描述: |

| DM74LS74A WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| DM74LS74AM | 功能描述:觸發(fā)器 Dl D-Type Flip-Flop RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時(shí)間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| DM74LS74AMX | 功能描述:觸發(fā)器 Dl D-Type Flip-Flop RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時(shí)間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。