- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄9561 > DS21348TN (Maxim Integrated Products)IC LIU LN T1/E1/J1 3.3V 44-TQFP PDF資料下載

參數(shù)資料

| 型號: | DS21348TN |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 8/76頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC LIU LN T1/E1/J1 3.3V 44-TQFP |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS |

| 產(chǎn)品變化通告: | Product Discontinuation 20/Feb/2012 |

| 標(biāo)準(zhǔn)包裝: | 160 |

| 類型: | 線路接口裝置(LIU) |

| 驅(qū)動器/接收器數(shù): | 1/1 |

| 規(guī)程: | T1/E1/J1 |

| 電源電壓: | 3.135 V ~ 3.465 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 44-TQFP |

| 供應(yīng)商設(shè)備封裝: | 44-TQFP(10x10) |

| 包裝: | 托盤 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

DS21348/DS21Q348

16 of 76

NAME

PIN

I/O

FUNCTION

TTIP/

TRING

34/37

O

Transmit Tip and Ring [TTIP AND TRING]. Analog line driver

outputs. These pins connect via a step-up transformer to the line. See

Section 5 for details.

VDD

21/36

—

Positive Supply. 3.3V ±5%

VSM

20

I

Voltage Supply Mode. Should be low for 3.3V operation.

VSS

22/35

—

Signal Ground

WR (R/W)

3

I

Write Input (Read/Write), Active Low. See the bus timing

diagrams in Section 11.

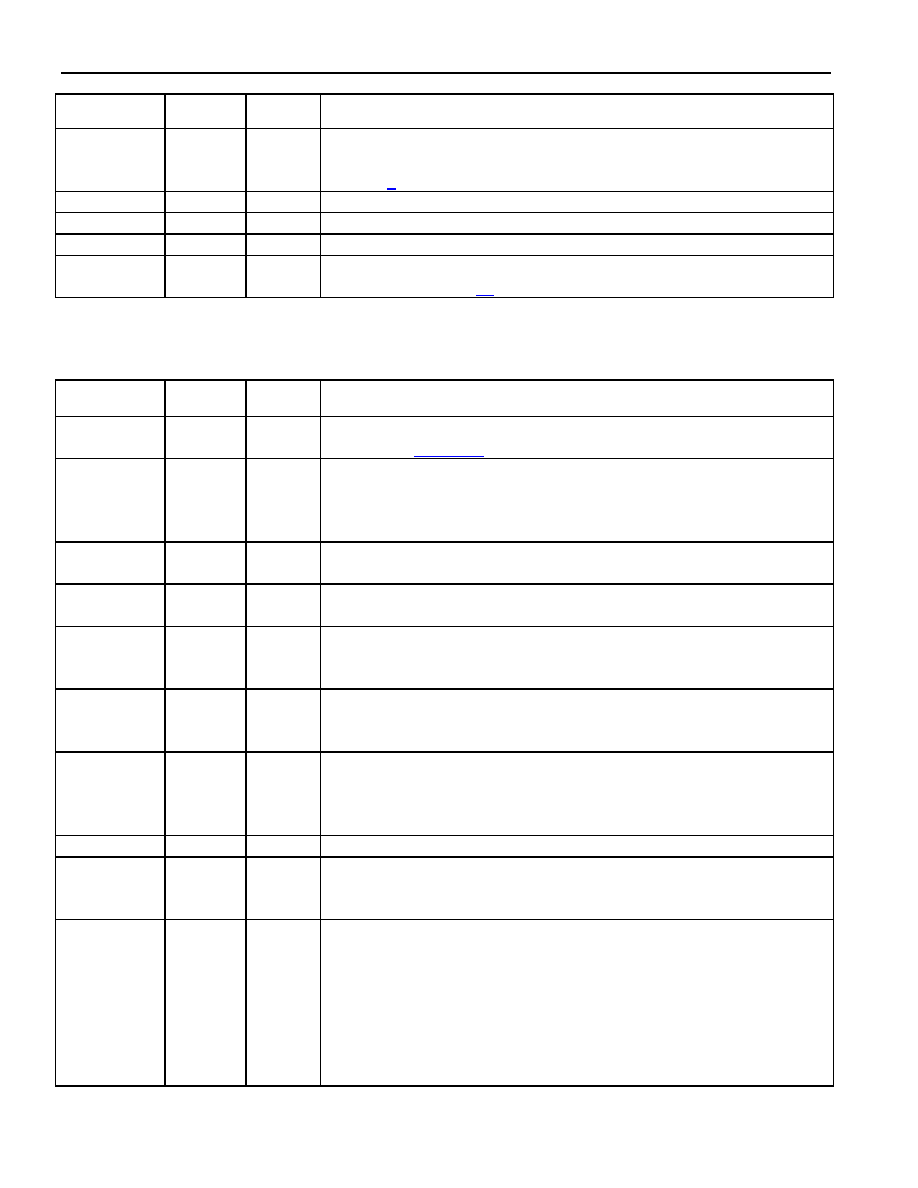

Table 2-6. Pin Descriptions in Serial Port Mode (Sorted By Pin Name,

DS21348T Pin Numbering)

NAME

PIN

I/O

FUNCTION

BIS0/BIS1

32/33

I

Bus Interface Select Bits 0 and 1. Used to select bus interface

option. See Table 2-1 for details.

BPCLK

31

O

Backplane Clock. A 16.384MHz, 8.192MHz, 4.096MHz, or

2.048MHz clock output that is referenced to RCLK selectable via

CCR5.7 and CCR5.6. In hardware mode, defaults to 16.384MHz

output.

CS

1

I

Chip Select, Active Low. Active-low signal must be low to read or

write to the device.

HRST

29

I

Hardware Reset, Active Low. Bringing

HRST low will reset the

DS21348 setting all control bits to their default state of all zeros.

ICES

8

I

Input Clock Edge Select. Selects whether the serial port data input

(SDI) is sampled on rising (ICES =0) or falling edge (ICES = 1) of

SCLK.

INT

23

O

Interrupt, Active Low. Flags host controller during conditions and

change of conditions defined in the Status Register. Active-low,

open-drain output.

MCLK

30

I

Master Clock. A 2.048MHz (±50ppm) clock source with TTL

levels is applied at this pin. This clock is used internally for both

clock/data recovery and for jitter attenuation. Use of a T1 1.544MHz

clock source is optional.

NA

—

I

Not Assigned. Should be tied low.

OCES

9

I

Output Clock Edge Select. Selects whether the serial port data

output (SDO) is valid on the rising (OCES = 1) or falling edge

(OCES = 0) of SCLK.

PBEO

24

O

PRBS Bit Error Output. The receiver will constantly search for a

215-1 or a 220-1 PRBS depending on the ETS bit setting (CCR1.7).

Remains high if out of synchronization with the PRBS pattern. Goes

low when synchronized to the PRBS pattern. Any errors in the

received pattern after synchronization will cause a positive going

pulse (with same period as E1 or T1 clock) synchronous with

RCLK. PRBS bit errors can also be reported to the ECR1 and ECR2

registers by setting CCR6.2 to a logic 1.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VI-23Z-MV-F4 | CONVERTER MOD DC/DC 2V 60W |

| VI-260-CU-B1 | CONVERTER MOD DC/DC 5V 200W |

| VI-25H-CU-B1 | CONVERTER MOD DC/DC 52V 200W |

| VI-23X-MX-F3 | CONVERTER MOD DC/DC 5.2V 75W |

| MS27484T16F35PD | CONN PLUG 55POS STRAIGHT W/PINS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS21348TN+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 3.3V E1/T1/J1 Line Interface RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21348TNB | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21348T-W | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21349 | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:3.3V T1/J1 Line Interface Unit |

| DS21349DK | 功能描述:網(wǎng)絡(luò)開發(fā)工具 DS21349 Design Kit RoHS:否 制造商:Rabbit Semiconductor 產(chǎn)品:Development Kits 類型:Ethernet to Wi-Fi Bridges 工具用于評估:RCM6600W 數(shù)據(jù)速率:20 Mbps, 40 Mbps 接口類型:802.11 b/g, Ethernet 工作電源電壓:3.3 V |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。