- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄377008 > DT28F160S3-120 (INTEL CORP) 16 Characters x 2 Lines, 5x7 Dot Matrix Character and Cursor PDF資料下載

參數(shù)資料

| 型號(hào): | DT28F160S3-120 |

| 廠商: | INTEL CORP |

| 元件分類: | DRAM |

| 英文描述: | 16 Characters x 2 Lines, 5x7 Dot Matrix Character and Cursor |

| 中文描述: | 1M X 16 FLASH 2.7V PROM, 120 ns, PDSO56 |

| 封裝: | 16 X 23.70 MM, SSOP-56 |

| 文件頁(yè)數(shù): | 30/52頁(yè) |

| 文件大?。?/td> | 1262K |

| 代理商: | DT28F160S3-120 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)當(dāng)前第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)

28F160S3, 28F320S3

E

30

ADVANCE INFORMATION

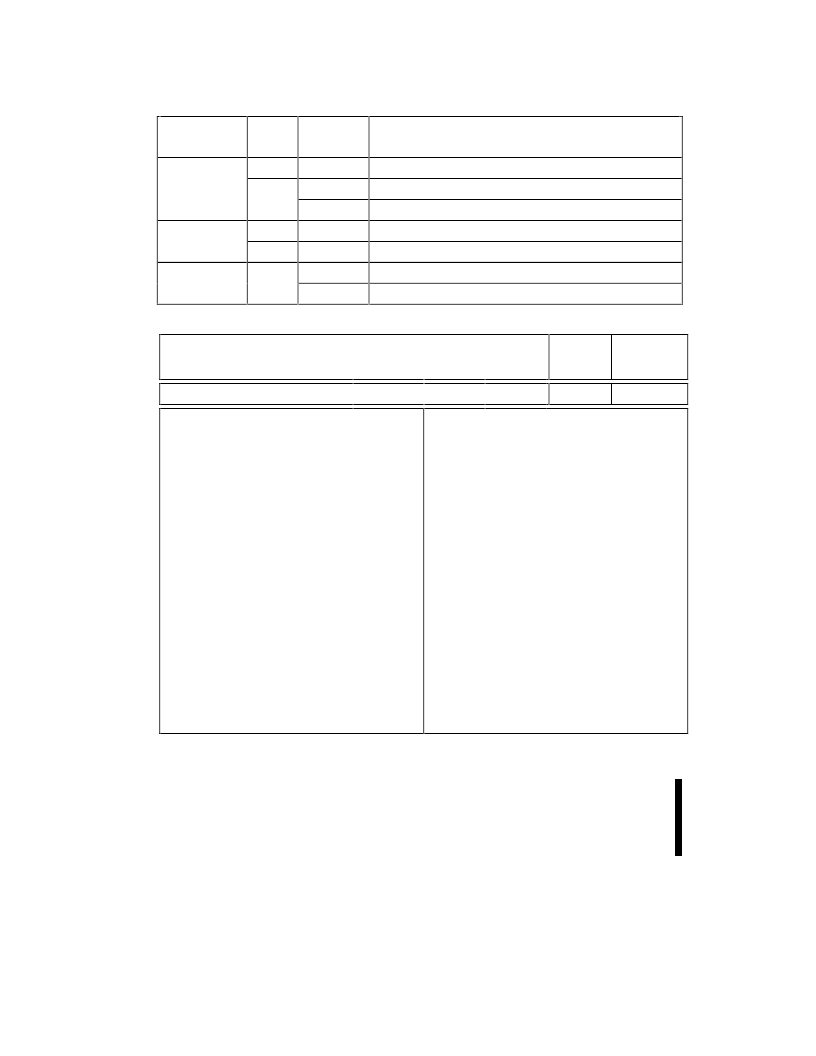

Table 13. Write Protection Alternatives

Operation

Block

Lock-

Bit

WP#

Effect

Program and

0

V

IL

or V

IH

Block erase and programming enabled

Block Erase

1

V

IL

Block is locked. Block erase and programming disabled

V

IH

Block Lock-Bit override. Block erase and programming enabled

Full Chip Erase

0,1

V

IL

All unlocked blocks are erased

X

V

IH

Block Lock-Bit override. All blocks are erased

Set or Clear

X

V

IL

Set or clear block lock-bit disabled

Block Lock-Bit

V

IH

Set or clear block lock-bit

enabled

Table 14. Configuration Coding Definitions

Reserved

Pulse on

Write

Complete

Pulse on

Erase

Complete

bits 7

–2

bit 1

bit 0

DQ7

–DQ2 = Reserved

DQ1/DQ0 = STS Pin Configuration Codes

00 = default, level mode RY/BY#

(device ready) indication

01 = pulse on Erase complete

10 = pulse on Flash Program complete

11 = pulse on Erase or Program Complete

Configuration Codes 01b, 10b, and 11b are all pulse

mode such that the STS pin pulses low then high

when the operation indicated by the given

configuration is completed.

Configuration Command Sequences for STS pin

configuration (masking bits D7–D2 to 00h) are as

follows:

Default RY/BY# level mode

ER INT (Erase Interrupt):

Pulse-on-Erase Complete

PR INT (Program Interrupt):

Pulse-on-Flash-Program Complete

ER/PR INT (Erase or Program Interrupt): B8h, 03h

Pulse-on-Erase or Program Complete

B8h, 00h

B8h, 01h

B8h, 02h

DQ7–DQ2 are reserved for future use.

default (DQ1/DQ0 = 00) RY/BY#, level mode

-----used to control HOLD to a memory controller to

prevent accessing a flash memory subsystem while

any flash device's WSM is busy.

configuration 01

-----used to generate a system interrupt pulse when

any flash device in an array has completed a block

erase or sequence of queued block erases. Helpful

for reformatting blocks after file system free space

reclamation or ‘cleanup’

ER INT, pulse mode

(1)

configuration 10

-----used to generate a system interrupt pulse when

any flash device in an array has complete a

program operation. Provides highest performance

for servicing continuous buffer write operations.

PR INT, pulse mode

(1)

configuration

-----used to generate system interrupts to trigger

servicing of flash arrays when either erase or flash

program operations are completed when a common

interrupt service routine is desired.

ER/PR INT, pulse mode

(1)

NOTE:

1.

When the device is configured in one of the pulse modes, the STS pin pulses low with a typical pulse width of 250 ns.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| dt31-2025at | Telecommunication HDSL Transformer |

| DT31-2026AT | Telecommunication HDSL Transformer |

| DT31-2031AT | Telecommunication HDSL Transformer |

| DT31-2032AT | Telecommunication HDSL Transformer |

| DT31N06KOF-A | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DT28F160S3-130 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:WORD-WIDE FlashFile MEMORY FAMILY |

| DT28F160S3-75 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:WORD-WIDE FlashFile MEMORY FAMILY |

| DT28F160S570 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:5 VOLT FlashFilea?¢ MEMORY |

| DT28F320J5120 | 制造商:INTEL 功能描述:_ |

| DT28F320J5-120 | 制造商:INTEL 功能描述:_ |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。